آموزش نرم افزار Vivado ، اگر به دنبال شروع کار با Xilinx Vivado Design Suite هستید، این آموزش برای شما مفید خواهد بود. اگر به دنبال راهی آسان برای شروع کار با PLD های شرکت Xilinx، یا حتی دیگر PLDها میگردید، در این صورت این آموزش همچنان می تواند برای شما مفید باشد، اما باید بپذیرید که از PLDهای Xilinx و Vivado Design Suite به عنوان مبنای کاری خود استفاده کنید.

این آموزش توسعه روی سخت افزار منطقی قابل برنامه ریزی واقعی را آموزش میدهد، این روش نه تنها راهی عملی برای یاد گرفتن، بلکه بنایی ضروری برای شروع کار روی برنامههای خودتان نیز میباشد.

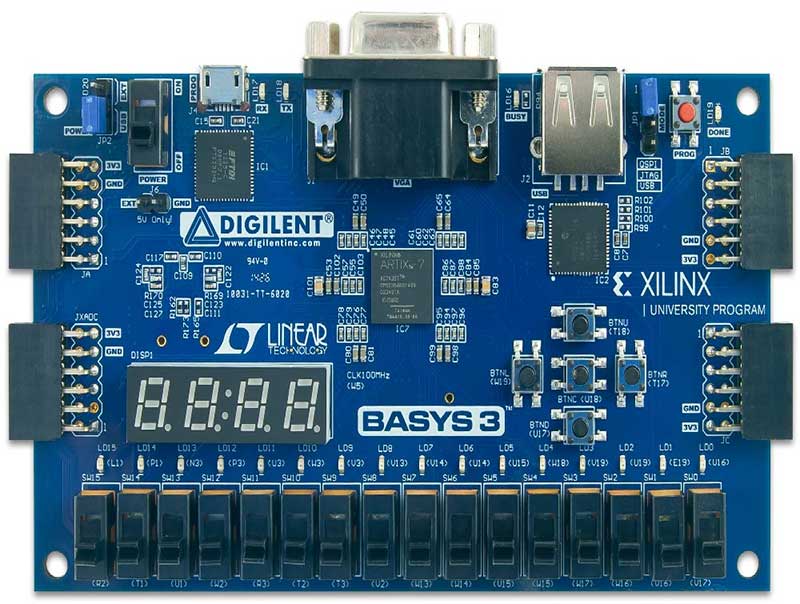

میتوانید از هر برد توسعهی PLDای (اکثر بردهای FPGA موجود در بازار الان ساپورت میکنن.) که با Vivado سازگار باشد استفاده کنید. در حال حاضر تمامی مدلهای جدیدتر Xilinx با Vivado کار میکنند که شامل سری7 و دستگاههای UltraScale میشود. برد Basys 3 شرکت Digilent برای مثالهای این آموزش و برای راحتی افراد تازهکار در زمینه PLD انتخاب شدهاست. در ادامه با میکرو دیزاینر الکترونیک همراه باشید تا آموزش نرم افزار Vivado را باهم پیش ببریم.

Digilent Basys 3 یک برد آموزشی برای کاربران مبتدی FPGA است که دارای یک تراشه Xilinx Artix-7 میباشد.

دانلود و نصب نرم افزار Vivado

Xilinx نسخهی رایگانی از Vivado Design Suite را به نام WebPACK عرضه میکند، همچنین این شرکت در صورت ثبت نام در وبسایت آنها و ارائهی اطلاعاتی پایه یک لایسنس نامحدود نیز برای WebPACK به شما ارائه میکند. شما میتوانید هم از وبسایت خود شرکت XILINX نسخه رایگان را دانلود کنید برای سیستم عامل مورد نظر و یا میتونید از وبسایت های فارسی نسخه کامل کرک شده را با سرچ ” دانلود VIVADO” به رایگان دانلود و نصب کنید.

قبل از شروع کار

- ابتدا باید Xilinx Vivado Design Suite را دانلود و نصب کنید. در صورت پشتیبانی نسخه رایگان WebPACK از PLD موردنظر شما این نسخه برای تکمیل این آموزش کافی است(از نسخهی 2015.4 WebPACK برای این آموزش استفاده شده است).

- شما به یک برد توسعهی مناسب نیز نیاز دارید.

- اگر از بردتوسعهای استفاده میکنید که نیاز به پروگرامر JTAG یا منبع تغذیهی خارجی دارد به طبع به این موارد نیاز احتیاج خواهید داشت. Basys 3 این لوازم را داخل خود دارد، اما اگر از برد دیگری استفاده میکنید برگههای اطلاعات فنی آن را برای اطلاعات بیشتر مطالعه کنید.

- شما باید پروگرامر JTAG و/یا برد توسعه خود را به کامپیوتر متصل کنید، آن را روشن کنید و درایورهای لازم را نصب کنید.

یک شروع ساده – منطق پایه و I/O

در اینجا بسیار ساده شروع خواهیم کرد، 3 پایه را به عنوان ورودی و 3پایه دیگر را به عنوان خروجی به همراه منطقی ساده بین آن ها معرفی میکنیم. برای مثال Basys 3 سه سوییچ اول برد (SW0-SW2) به ورودیها و سه LED اول (LD0-LD2) به خروجیها متصل میشوند.

ساخت یک پروژه جدید در نرم افزار Vivado

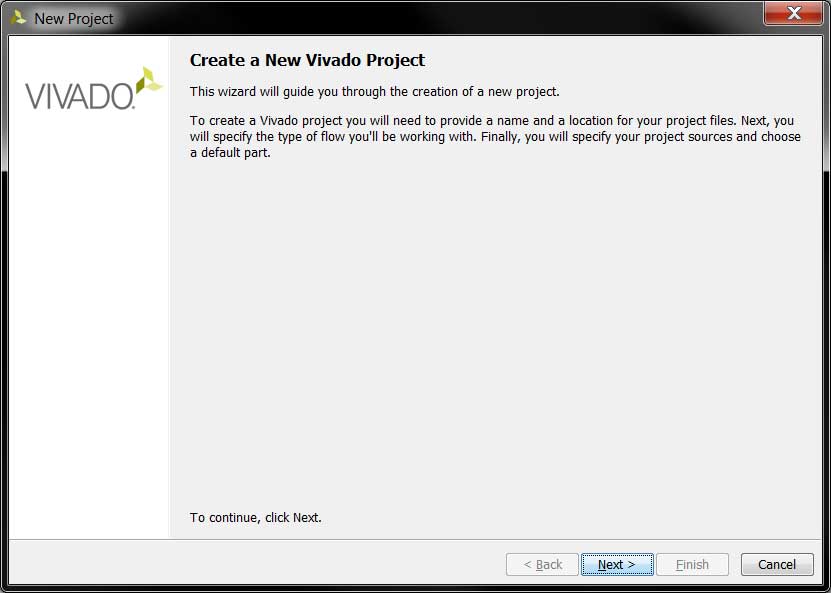

بعد از بازکردن Vivado، از صفحهی startup روی آیکن “Create New Project” کلیک کنید. همچنین میتوانید از منوی File گزینهی New Project را نیز انتخاب کنید.

راهنمای پروژهی جدید باز خواهد شد.، برای ادامه دکمهی “Next >” را فشار دهید.

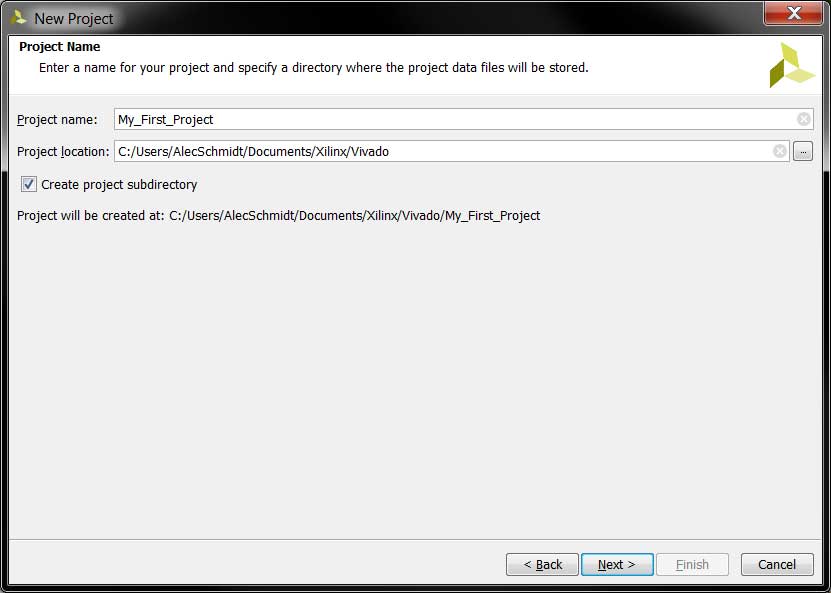

نام پروژه را وارد کنید و محل آن را تعیین کنید. در هیچ کدام از آنها از فاصله استفاده نکنید. میتوانید فقط از حرف، عدد و underline استفاده کنید. در صورت نیاز در درایو اصلی کامپیوترتان یک دایرکتوری جدید برای پروژههای Xilinx Vivado ایجاد کنید(برای مثال C:\Vivado). همچنین بهتر است همیشه تیک گزینهی “Create project sub-directory” را نیز بزنید. این گزینه با ساخت یک دایرکتوری برای هر پروژه همه چیز را مرتب نگه میدارد و به جلوگیری از ایجاد مشکل کمک میکند. برای ادامه دکمهی “Next >” را بزنید.

گزینهی “RTL Project” و تیک “Do not specify sources at this time” را بزنید. اگر این تیک را نزنید راهنما شما را به مراحل بیشتری برای اضافهکردن فایلهای از قبل موجود مانند سورس فایلهای VHDL یا Verilog، IP block های Vivado، و فایلهای constraint با پسوند .XDC برای تنظیمات پایهها و زمانبندی میبرد. برای این پروژه که اولین است، موارد موردنیاز را بعدا اضافه خواهیم کرد. برای ادامه دکمهی “Next >” را بزنید.

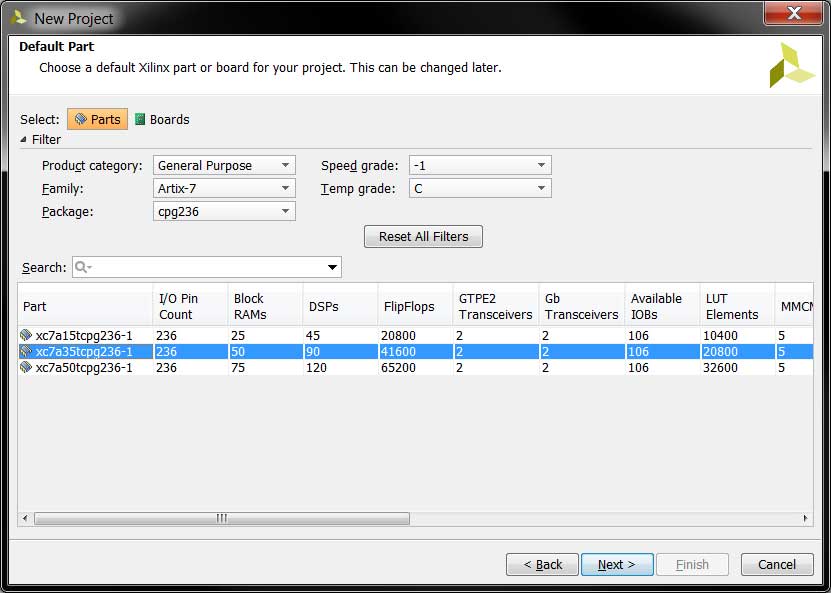

برای انتخاب پارت نامبر مشخص برای پروژهتان باید گزینهها را فیلتر کنید. میتوانید به طور فیزیکی اعداد روی چیپتان را بخوانید یا به اسناد بردتان برای پیدا کردن پارت نامبر رجوع کنید. در مورد Basys 3 چیپ Atrix-7 روی برد قرار دارد، و فیلترهای نشان داده شده به شما کمک میکنند تا دیوایس موردنظر که در عکس هایلایت شده است را انتخاب کنید. بعد از انتخاب دیوایس برای ادامه دکمهی “Next >” را فشار دهید.

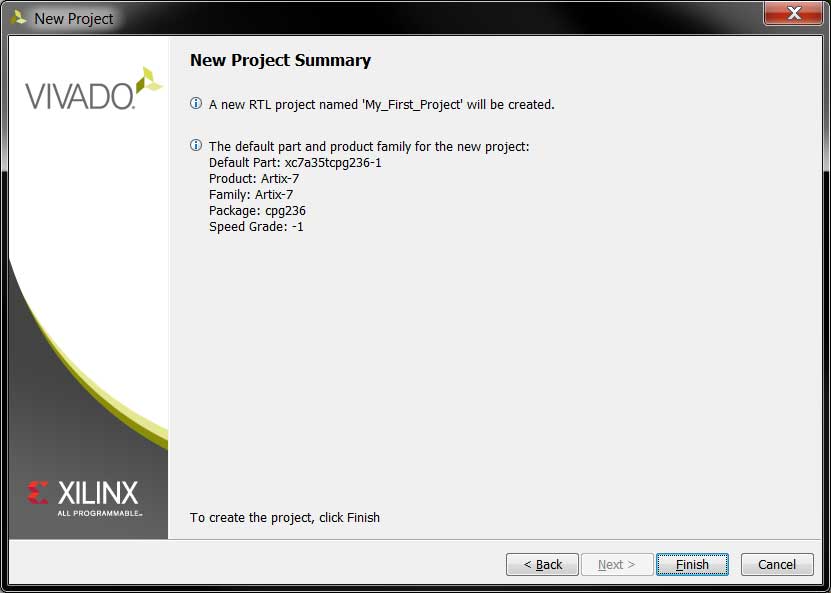

دکمهی “Finish” را بزنید تا Vivado پروژه شما را طبق شرایط تعیین شده ایجاد کند.

پیش رفتن با روند پروژه در نرم افزار Vivado

خب دمتونگر تا اینجای آموزش نرم افزار Vivado خوب پیش اومدیم الان پنجرهی پروژهی Vivado حاوی مقدار زیادی اطلاعات است که میتوانند بسته به اینکه در کدام مرحله از روند طراحی هستید تغییر کنند. این نکته را طی مطالعه این مطلب به خاطر داشته باشید، زیرا اگر یک زیر-پنجرهی مشخص یا تب زیر-پنجرهی مشخص را نمیتوانید ببینید احتمالا در قسمت درستی از طراحی نیستید.

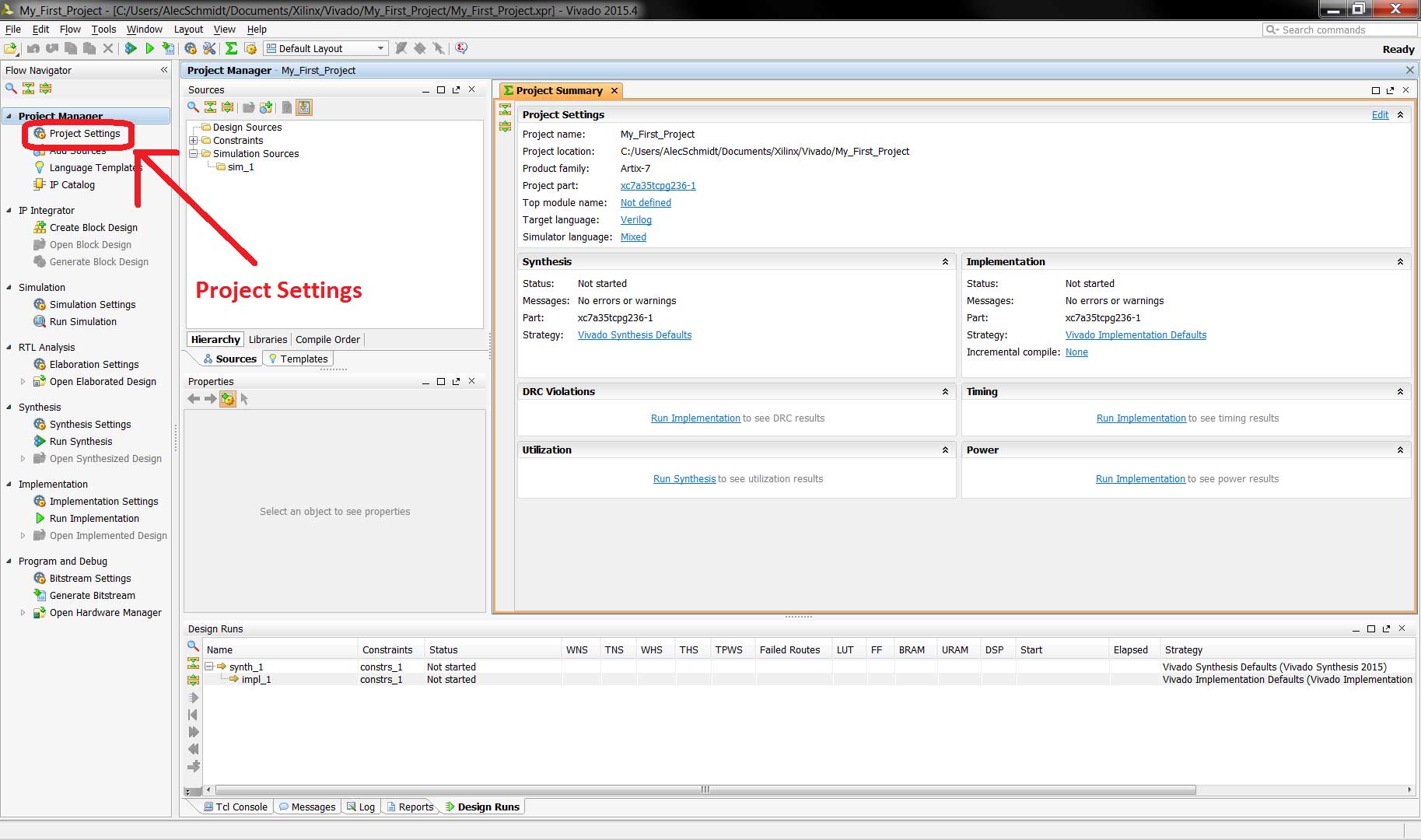

“Flow Navigator” در سمت چپ صفحه تمامی مراحل مختلف پروژه را از بالا به پایین به ترتیب نظم کرونولوژیکشان مرتب کرده است. شما از قسمت “Project manager” flow شروع میکنید و که هدر بالای صفحه کنار Flow Navigator نیز این مطلب را نشان میدهد. این هدر و بخش هایلایت شدهی مرتبط با آن در Flow Navigator به شما میگویند که کدام بخش از طراحی در حال حاضر باز است.

قسمت Project Manager

با کلیک روی “Project Settings” در قسمت Project Manager بخش Flow Navigator شروع کنید.

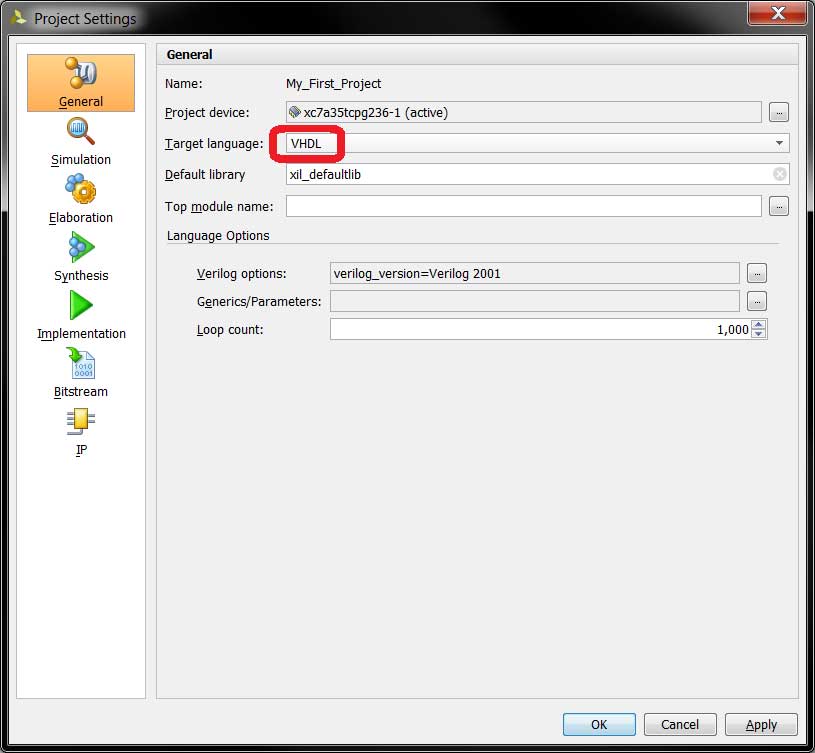

در این قسمت تنظیمات زیادی برای تمامی مراحل پروژه وجود دارد، اما اکنون فقط از منوی “Target Language” در قسمت “General” گزینه “VHDL” را انتخاب کنید و دکمهی “OK” را بزنید.

اضافه کردن سورس Add Sources

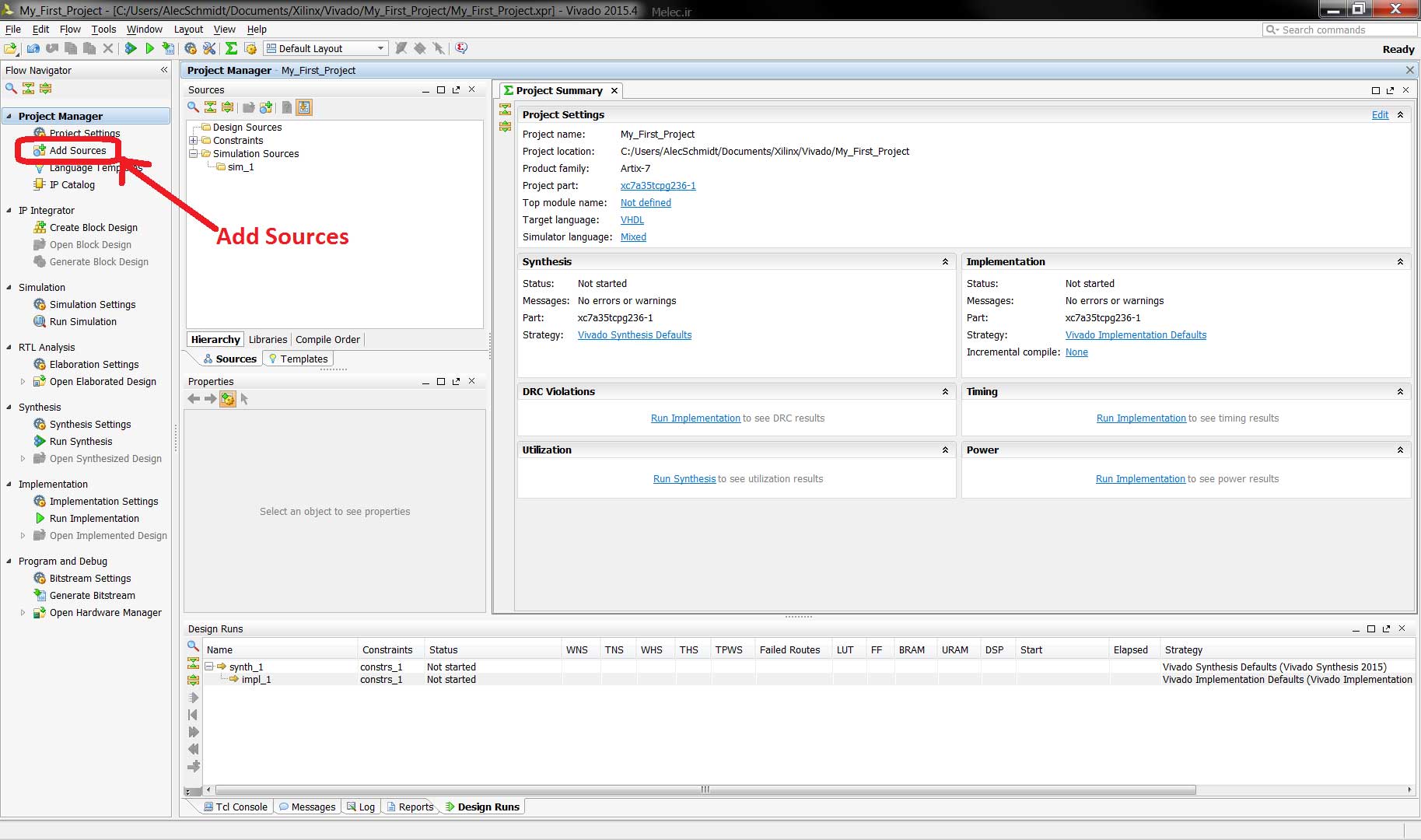

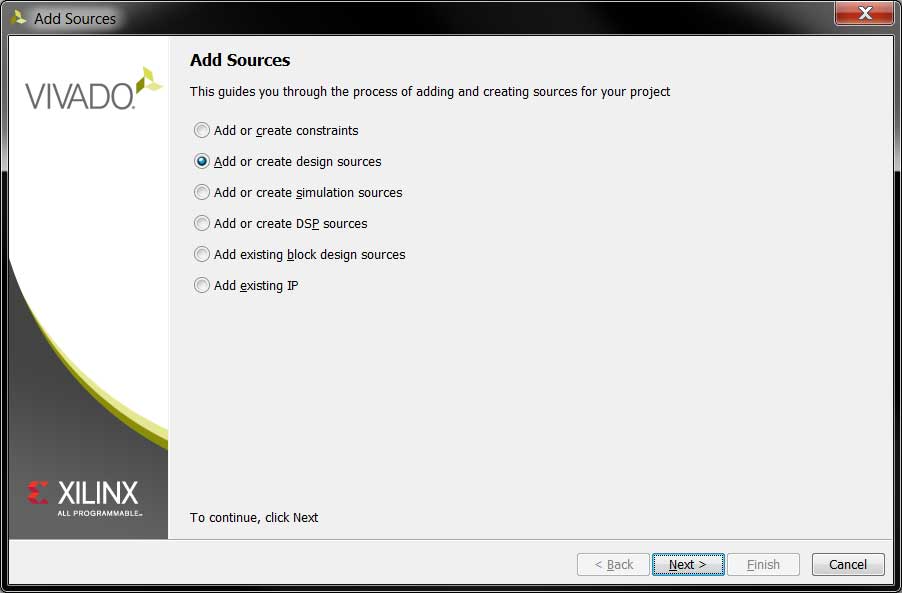

اکنون روی “Add Sources” در قسمت Project Manager بخش Flow Navigator کلیک کنید.

گزینهی “Add or create design sources” را انتخاب کنید و سپس دکمهی “Next >” را بزنید.

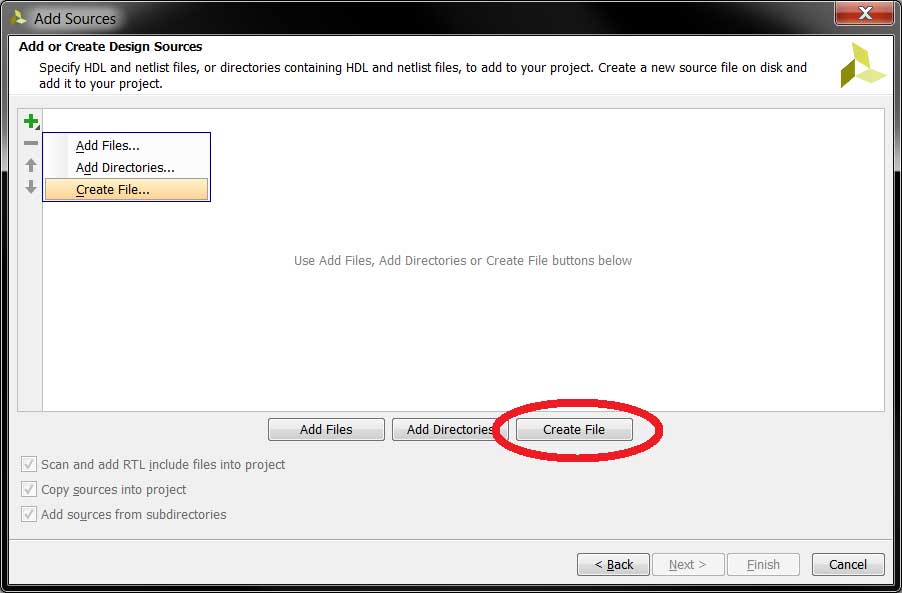

دکمهی “Create File” را بزنید یا علامت “+” سبز رنگ در گوشهی بالا سمت چپ را فشار دهید و گزینهی “Create File…” را انتخاب کنید.

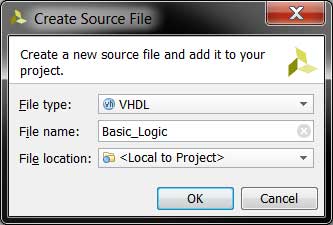

مطمئن شوید گزینههای نشان داده شده در پنجرهی “Create Source File” انتخاب شدهاند، و برای همگام بودن با آموزش برای “File Name” عبارت “Basic_Logic” را وارد کنید. سپس دکمهی “OK” را بزنید.

معمولا میتوانید هر اسمی را در صورت معتبر بودن برای “File Name” انتخاب کنید، اما همیشه اطمینان حاصل کنید که هیچ فاصلهای در آن نباشد.

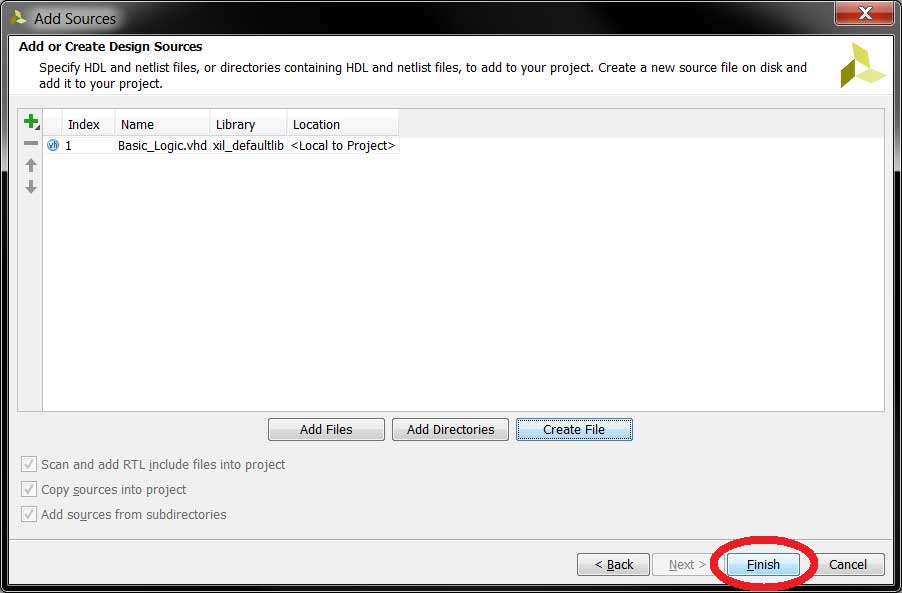

دکمهی “Finish” را بزنید تا Vivado پنجرهی “Define Module” را باز کند.

تعیین ماژول Define Module

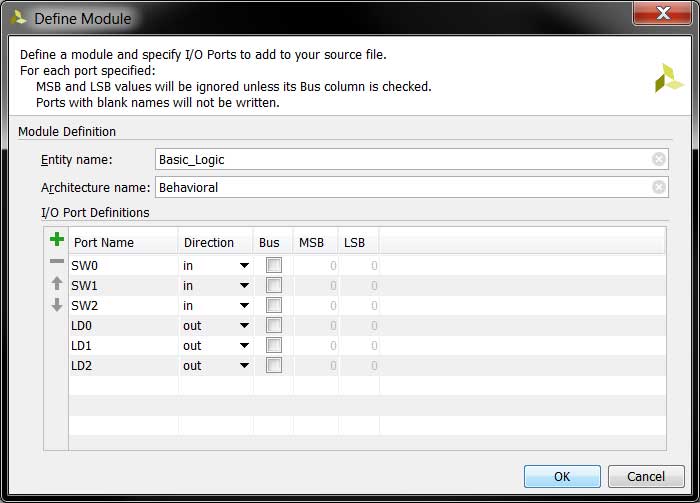

میتوانید از پنجرهی “Define Module” برای نوشتن بخشی از کد VHDL به طور خودکار استفاده کنید. مورد “I/O Port Definitions” میتواند با کلیک روی نماد “+” سبز در قسمت بالایی سمت چپ یا با کلیک کردن روی خط خالی بعدی اضافه شود. “Entity name” و “Architecture name” به ترتیب شناسههای VHDL استفاده شده در کد هستند، همچنین هر چیزی که برای هر “Port name” تایپ میشود. از هر شناسهی VHDL معتبری میتوان برای هریک از این موارد استفاده کرد، اما برای همگام بودن با آموزش اصلاعات را مانند موارد نشان داده شده وارد کنید. از درست بودن “Direction” های هرمورد اطمینان حاصل کنید. بعد از اتمام کار روی “OK” کلیک کنید.

توجه داشته باشید که اگر میخواهید خودتان کد را از اول بنویسید میتوانید دکمهی “Cancel” را بزنید و Vivado یک سورس فایل VHDL خالی درون پروژهی شما ایجاد میکند. اگر دکمهی “OK” را بدون تعریف کردن هیچ “I/O Port Definitions” بزنید Vivado همچنان ساختار کد VHDL پایه را مینویسد اما port definition خالی و به صورت کامنت شده میماند تا بعدا آن را از کامنت درآورده و تکمیل کنید.

همچنین دقت کنید که port nameهای اینجا با نشان دهندههای مرجع سیلک اسکرین سوییچها و LEDهای روی برد Basys 3 همخوانی دارند. این کار به دلیل راحتی دنبال کردن آموزش با برد Basys 3 است اما نباید توسط مبتدیان به عنوان یک قانون انگاشته شود; هر نام یک شناسه دلخواه است.

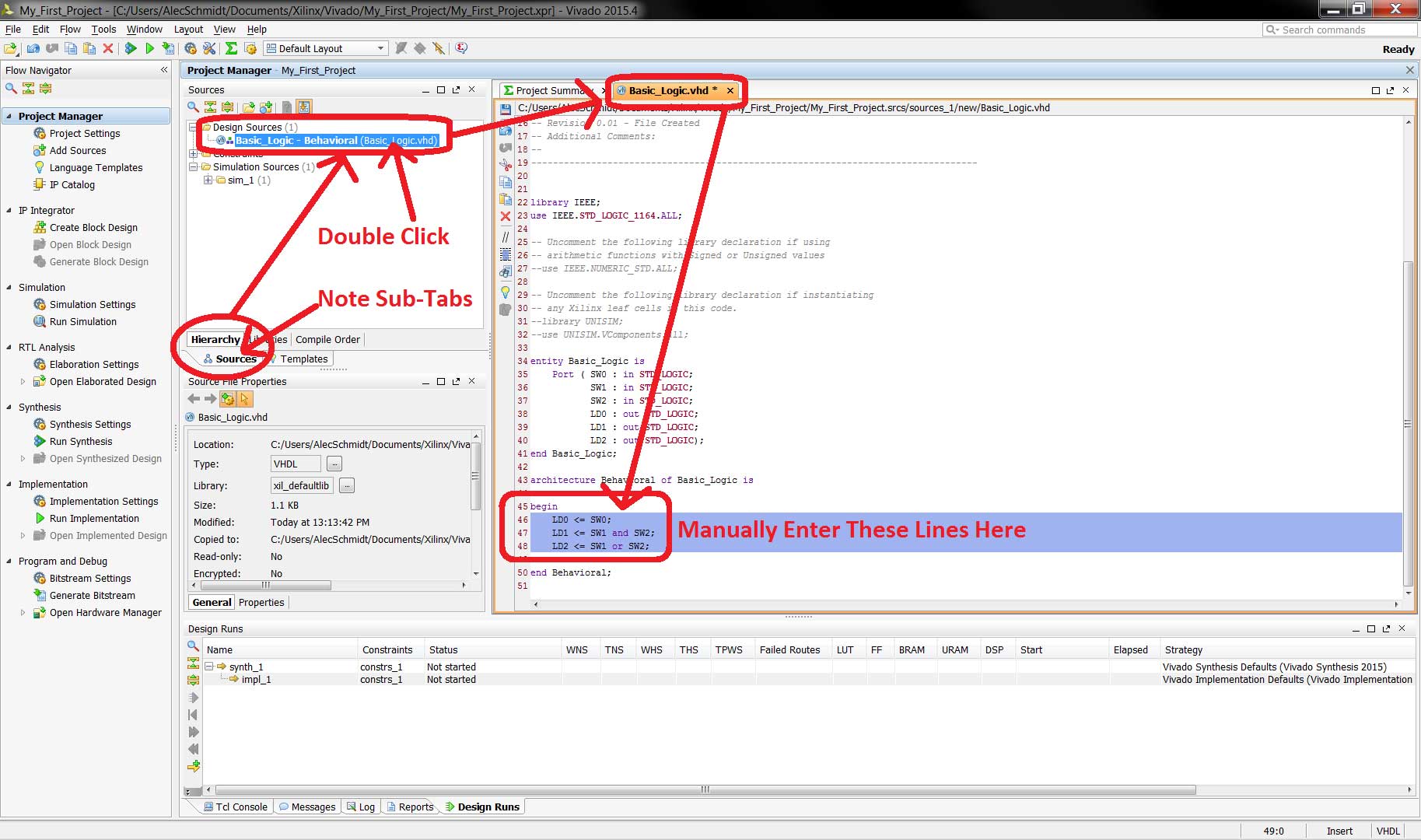

سورس فایل VHDL ساخته شده در فولدر “Design Sources” مانند تصویر به پروژهی شما اضافه میشود. روی آن دوبار کلیک کنید تا در یک تب جدید باز شود تا بتوانید آن را مشاهده یا ویرایش کنید. تمامی کد این بخش توسط پنجره قبلی “define Module” تولید شده است، و برای این مثال تنها نیاز دارید تا سه خط هایلایت شده را بین کلمات کلیدی “begin” و “end” وارد کنید.

آن سه خط این عبارات هستند:

LD0 <= SW0; LD1 <= SW1 and SW2; LD2 <= SW1 or SW2;

این راهنما قرار نیست آموزش VHDL باشد، و خطوط بالا نیز بسیار ساده هستند، اما برای افراد مبتدی در VHDL رفتار مورد انتظار از دستگاه به اختصار به شرح زیر است:

- خط اول تنها ورودی “SW0” را مستقیما به خروجی “LD0” منسوب میکند(یک بافر).

- خط دوم “و” منطقی ورودیهای “SW1” و “SW2” را به خروجی “LD1” مرتبط میکند(یک گیت AND).

- خط سوم “یا”ی منطقی ورودیهای “SW1” و “SW2” را به خروجی “LD2” متصل میکند(یک گیت OR).

بعد از این که این خطوط را به درستی وارد کردید، از منوی بالایی Vivado گزینهی File و سپس Save File را انتخاب کنید.

تحلیل RTL

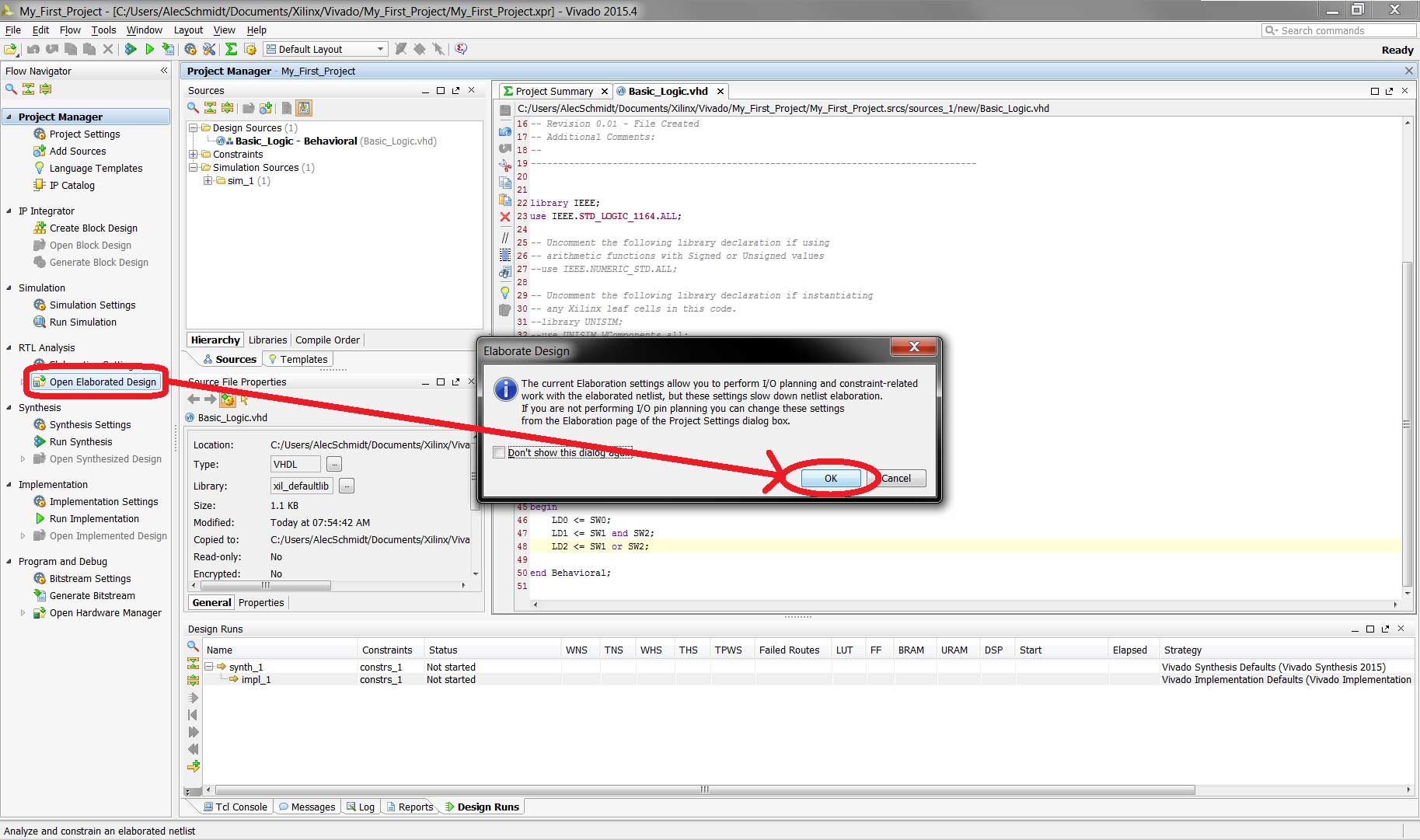

اکنون روی گزینهی “Open Elaborated Design” در مرحله تحلیل RTL بخش Flow Navigator کلیک کنید. ممکن است یک پنجره پیام برای شما پدیدار شود، در اینصورت دکمهی “OK” را بزنید. Vivado بعد از مقداری محاسبات Elaborated Design را باز خواهد کرد.

دقت کنید که اکنون فاز “RTL Analysis” در Flow Navigator هایلایت شده است و هدر کنار آن از “Project Manager” به “Elaborate Design” تغییر پیدا کرده است تا مرحلهای از طراحی که باز است و پنجرههای مربوط به آن را نشان دهد. اگر بین مراحل “Project Manager” و “RTL Analysis” از Flow Navigator سوییچ کنید مشاهده خواهید کرد که پنجرهها و هدر نیز متناسب با مرحله تغییر میکنند.

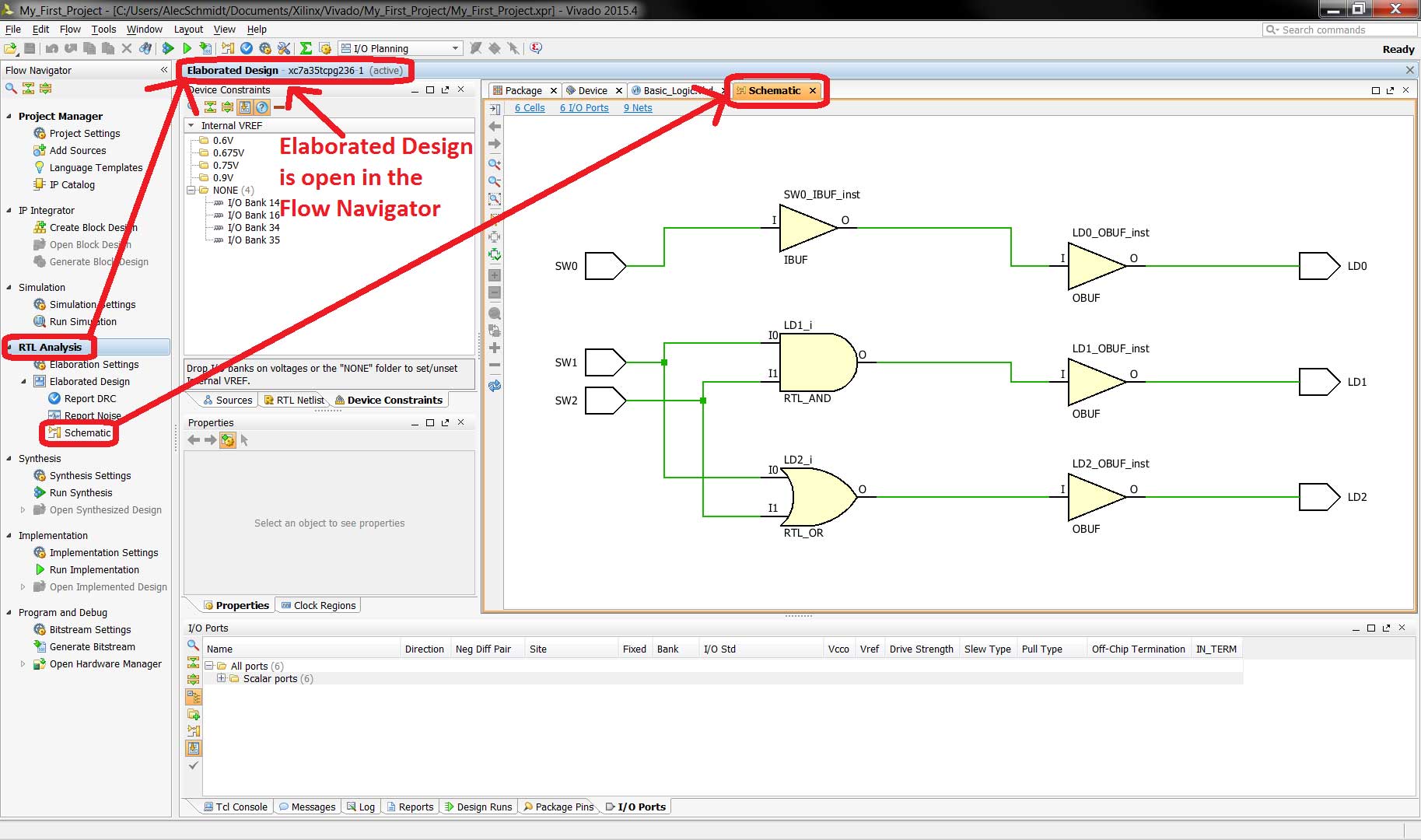

مشاهده شماتیک

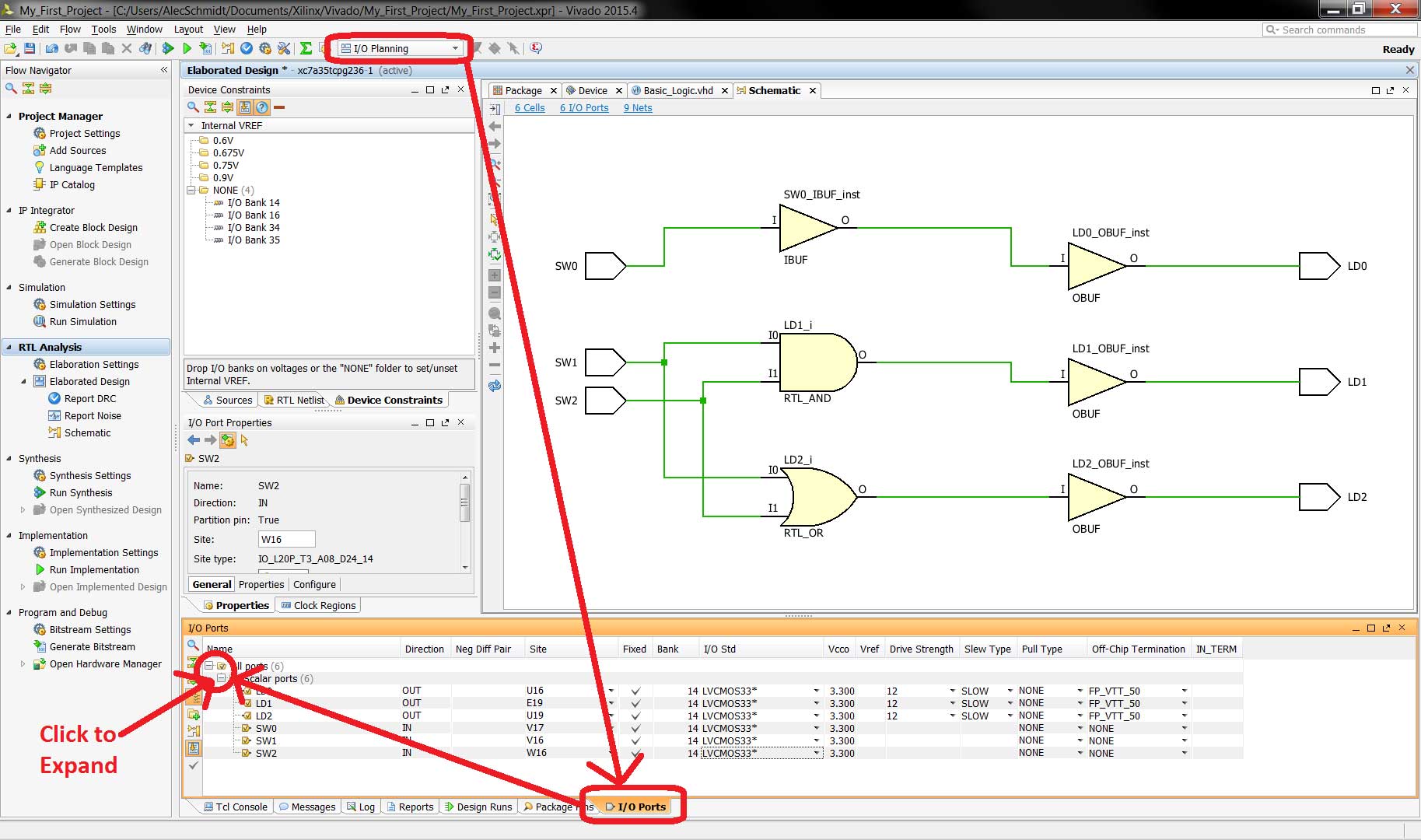

میتوانید روی دکمهی “Schematic” در مرحلهی RTL Analysis در Flow Navigator کلیک کنید تا یک تب که شماتیک کد VHDL نوشته را نشان میدهد باز شود.

تخصیص پایه های دستگاه

اکنون با پنجره Elaborate Design باز می توانید به تخصیص پایههای PLD خود بپردازید. گزینهی “I/O Planning”را از نوار ابزار بالایی انتخاب کنید، سپس مطمئن شوید که تب “I/O Ports” را در پایین صفحه مشاهده میکنید و روی ان کلیک کنید تا بزرگنمایی شده و تمامی پورتهای موجود را ببینید.

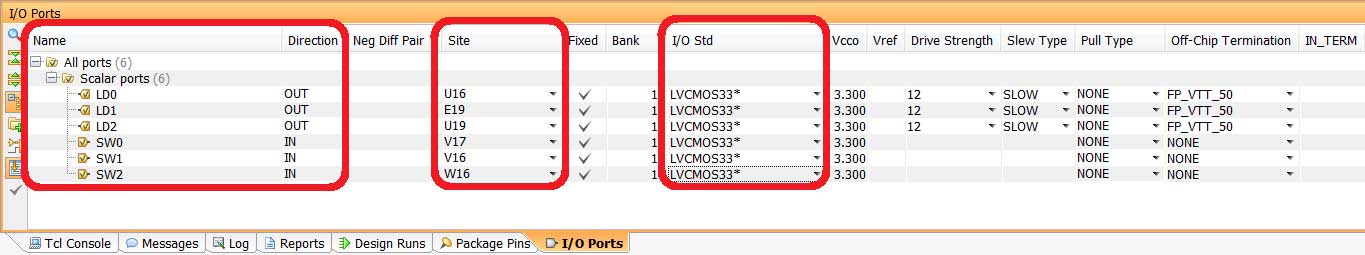

نام پورت ها و جهتهای آنها با کد VHDL واردشده همخوانی دارد. شما باید یک “Site” برای هرکدام تایپ کنید یا از گزینههای موجود انتخاب کنید تا یک پایهی فیزیکی معتبر از PLD به آن اختصاص دهید. همچنین باید به هر پایه انتخاب شده “I/O Std” مناسب را نیز اختصاص دهید تا با ریل تغذیه بانک I/O بردتان همخوانی داشته باشد.

برای افرادی که با برد Basys 3 پیش میآیند، اختصاصهای “Site” برای هر پین با سیلک اسکرین روی برد یکسان است، و تمامی انتخابهای “I/O Std” باید “LVCMOS33” باشند.

بعد از واردکردن تمامی موارد، از منوی بالایی Vivado گزینهی File و سپس Save Constraints را بزنید.

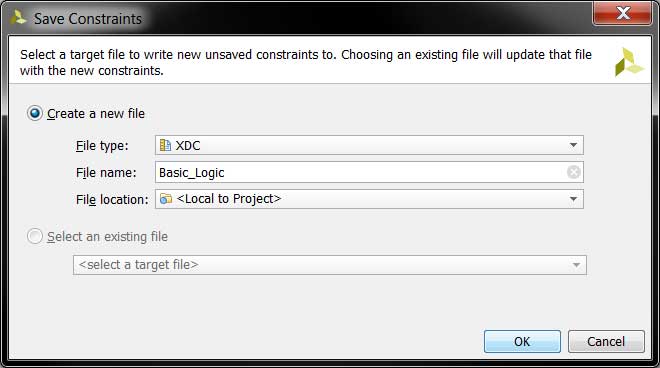

ساخت فایل Constraints

در پنجره “Save Constraints” تمامی گزینههای نشان داده شده در شکل را انتخاب کنید، و برای همگام بودن با آموزش “File Name” را “Basic_Logic” وارد کنید. بعد از اتمام دکمهی “OK” را بزنید.

معمولا میتوانید هر اسمی را در صورت معتبر بودن برای “File Name” انتخاب کنید، و همچنین نیازی نیست که با نام فایل HDL مانند اینجا یکی باشد، اما همیشه اطمینان حاصل کنید که هیچ فاصلهای در آن نباشد.

فایل Constraints میتواند با دوبار کلیک روی آن در زیر-تب “Sources” از پنجرهی “Sources” مشاهده و به صورت دستی ویرایش شود. میتوانید آن را برای مشاهده باز کنید، اما فعلا آن را ویرایش نکنید.

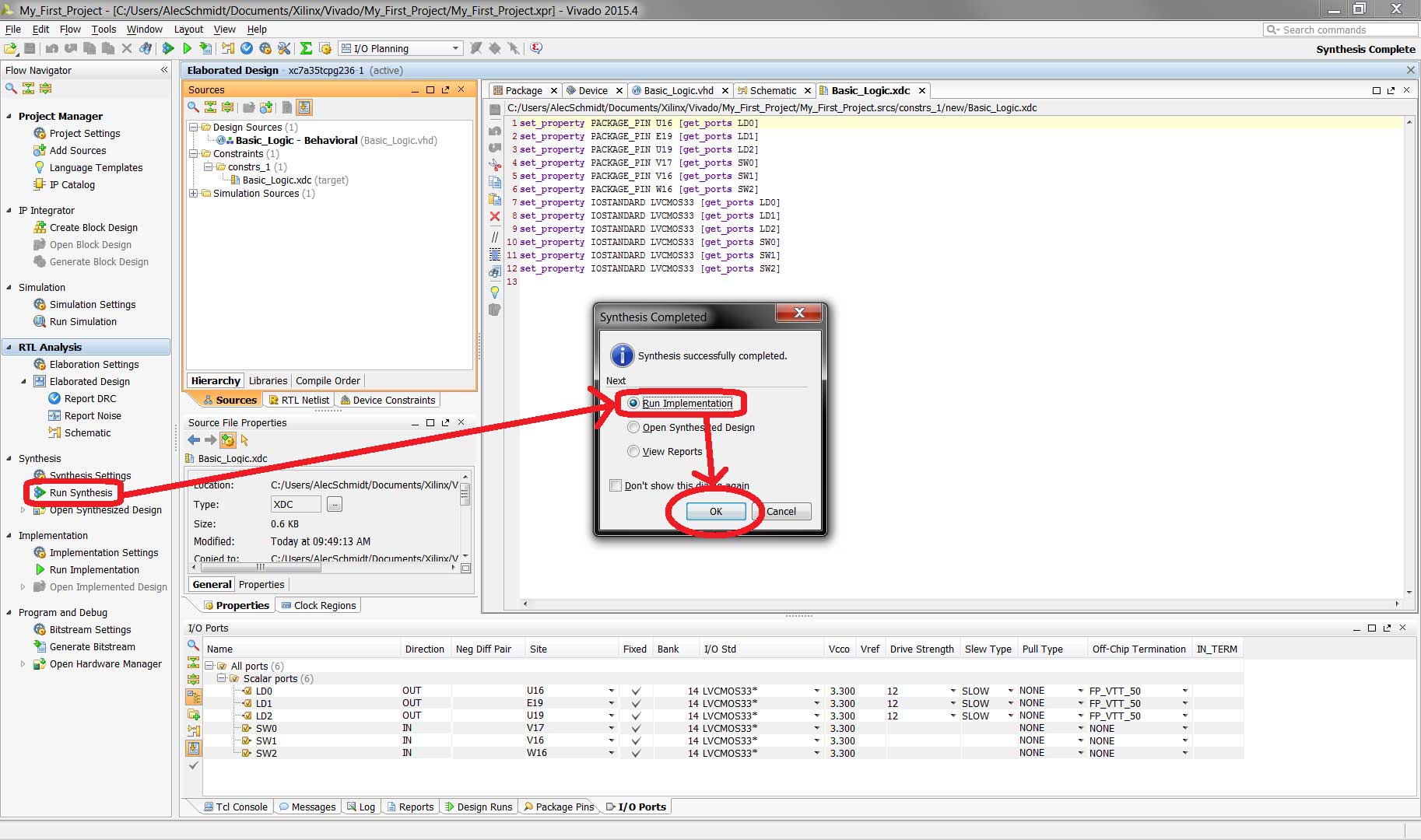

Synthesis و Implementation

اکنون در قسمت Synthesis از Flow Navigator گزینهی “Run Synthesis” را فشار دهید. مدتی طول میکشد تا Vivado پردازش را انجام دهد. اگر پیغام “Synthesis Completed” را دریافت کردید، گزینهی “Run Implementation” را انتخاب کنید و دکمهی “OK” را بزنید. همچنین میتوانید بعد از تکمیل شدن سنتز روی “Run Implementation” در قسمت Implementation از Flow Navigator کلیک کنید. این کار برای Vivado مدتی طول میکشد تا تکمیل شود.

پروگرام کردن و عیب یابی

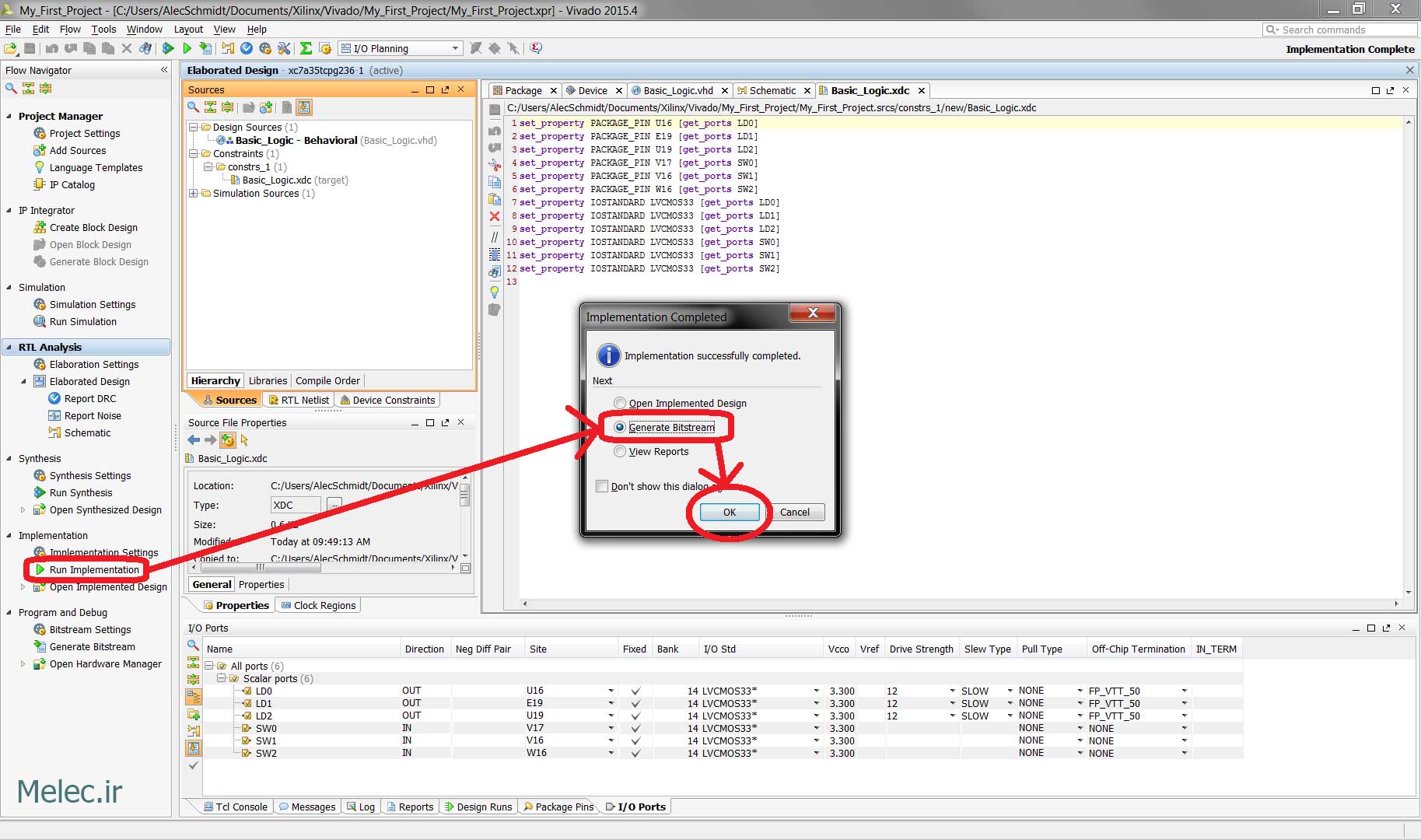

اگر پیام “Implementation Completed” نمایش داده شد، گزینهی “Generate Bitstream” را انتخاب کنید و “OK” را بزنید. همچنین میتوانید بعد از تکمیل شدن Implementation روی “Generate Bitstream” در قسمت Program and Debug از Flow Navigator کلیک کنید.

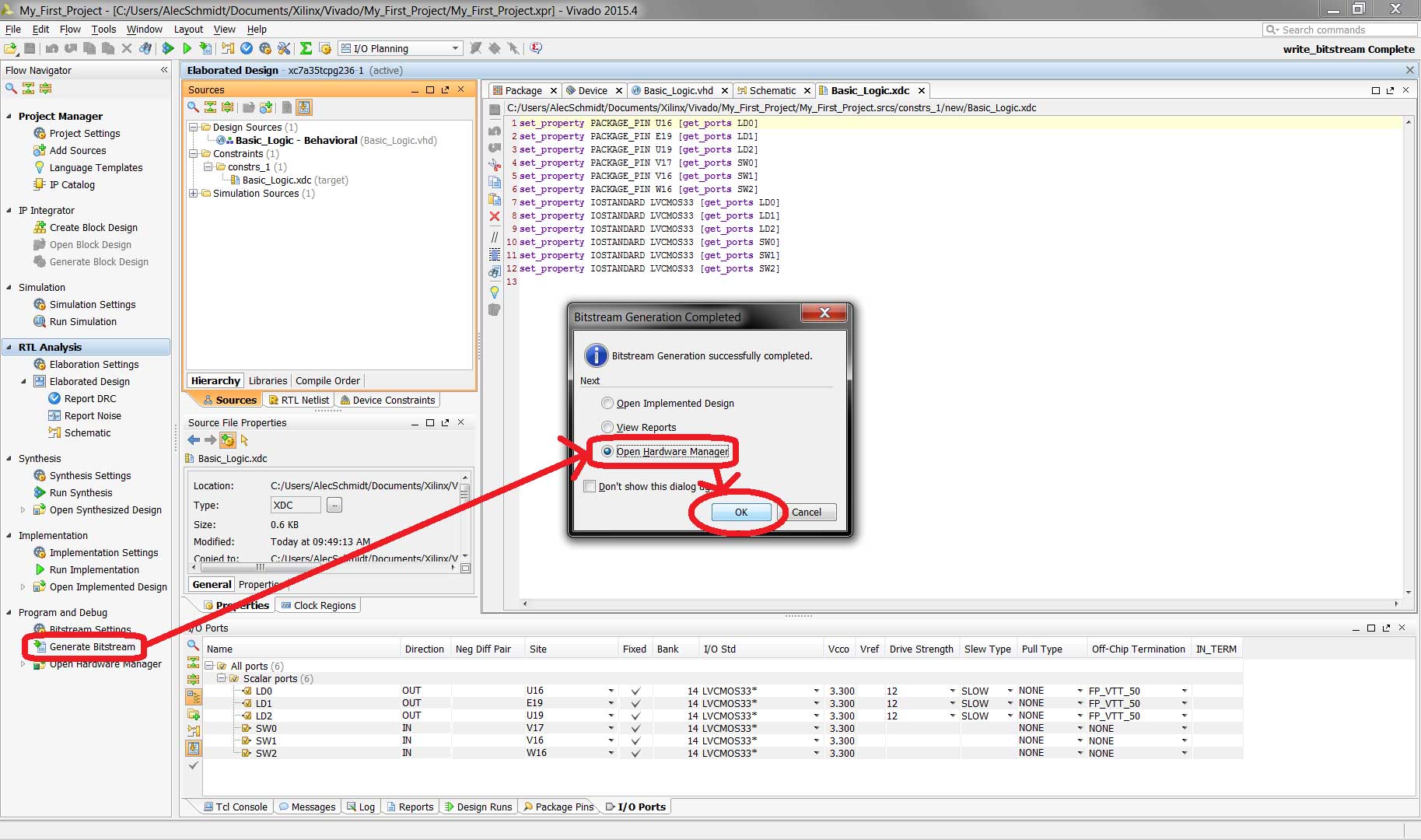

اگر پیام “Bitstream Generation Completed” را دریافت کردید، گزینهی “Open Hardware Manager” را انتخاب کنید و “OK” را بزنید. همچنین میتوانید بعد از تکمیل شدن Bitstream Generation روی “Open Hardware Manager” در قسمت Program and Debug از Flow Navigator کلیک کنید.

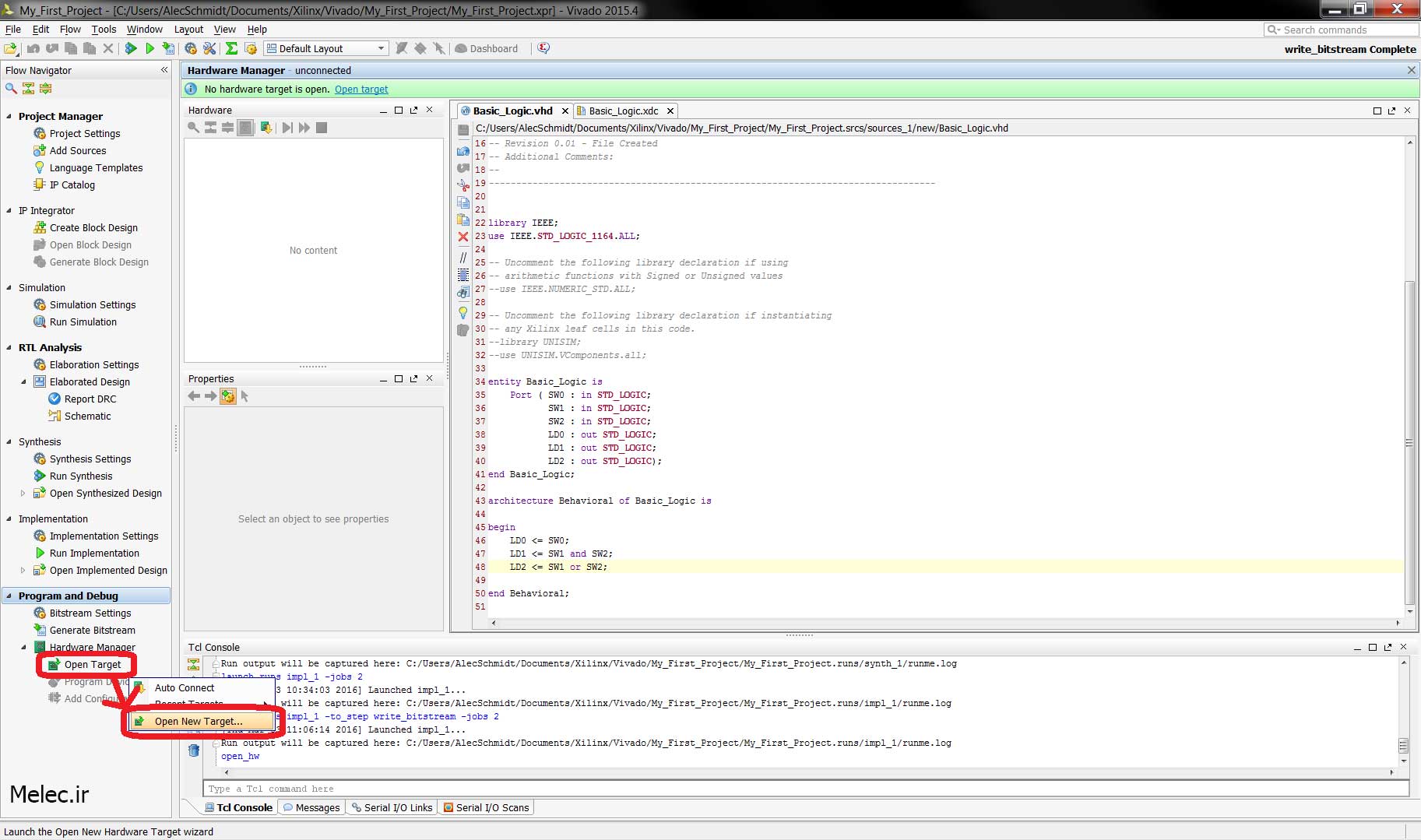

Open Target

اکنون روی “Open Target” در قسمت Debug and Program از Flow Navigator کلیک کنید و سپس “Open New Target…” از منویی که در ادامه باز میشود. در این مرحله باید از قبل پروگرامر JTAG و/یا برد توسعه خود را به کامپیوتر متصل کرده، آن را روشن کرده، و درایورهای موردنیاز را نصب کرده باشید.

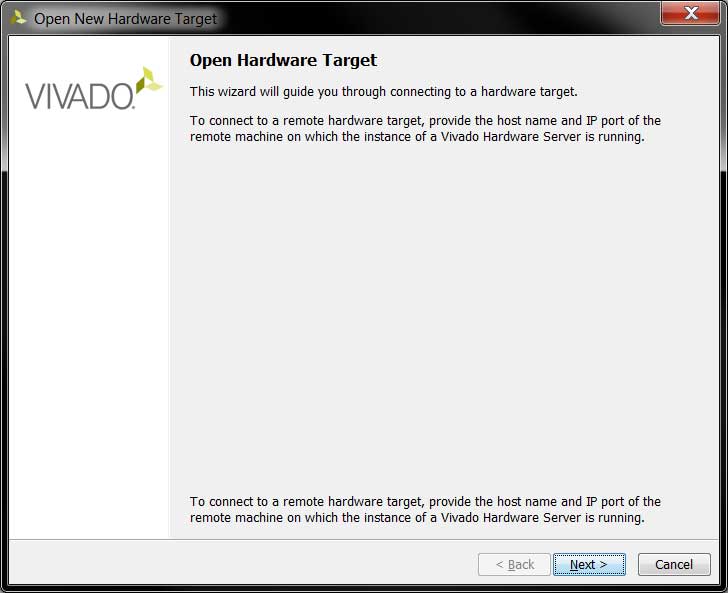

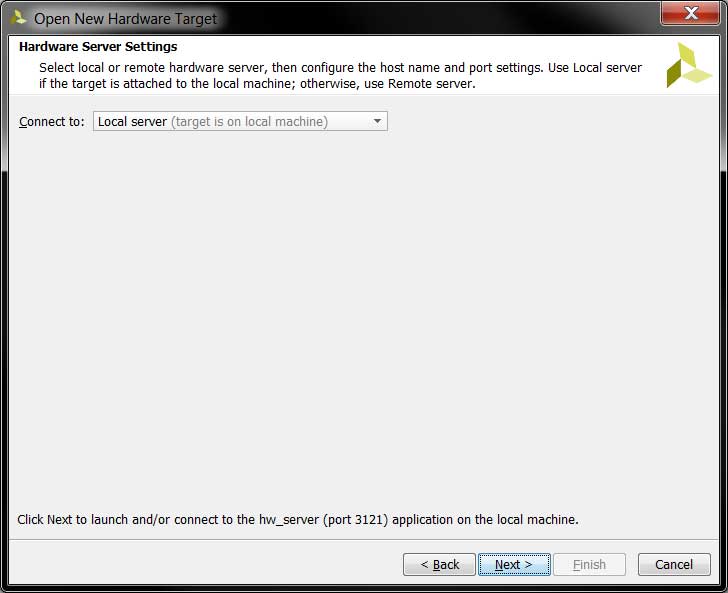

اکنون راهنمای Open New Target اجرا میشود، برای ادامه دکمهی “Next >” را بزنید.

از منوی نشان داده شده “Local Server (target is on local machine)” را انتخاب کنید و سپس برای ادامه دکمهی “Next >” را بزنید. Vivado اکنون به دنبال دستگاههای معتبر متصل به کامپیوتر خواهد گشت.

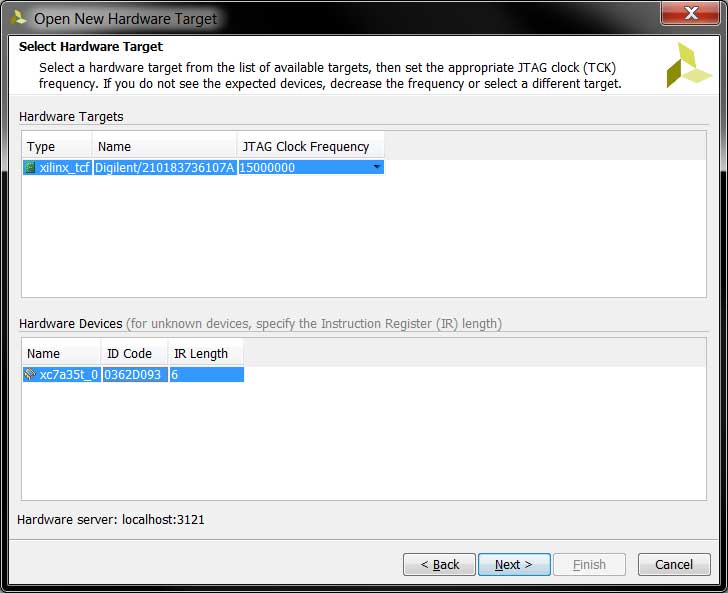

اگر همه چیز به درستی پیش رود چیزی شبیه به تصویر با نام سخت افزار خودتان مشاهده خواهید کرد. JTAG Hardware target و PLD موردنضر خود را انتخاب کنید و دکمهی “Next >” را بزنید. توجه داشته باشید که میتوانید “JTAG Clock Frequency” را تغییر دهید، اما منطقی است که با مقدار پیشفرض شروع کنید و بعدا در صورت نیاز تغییرات را اعمال کنید.

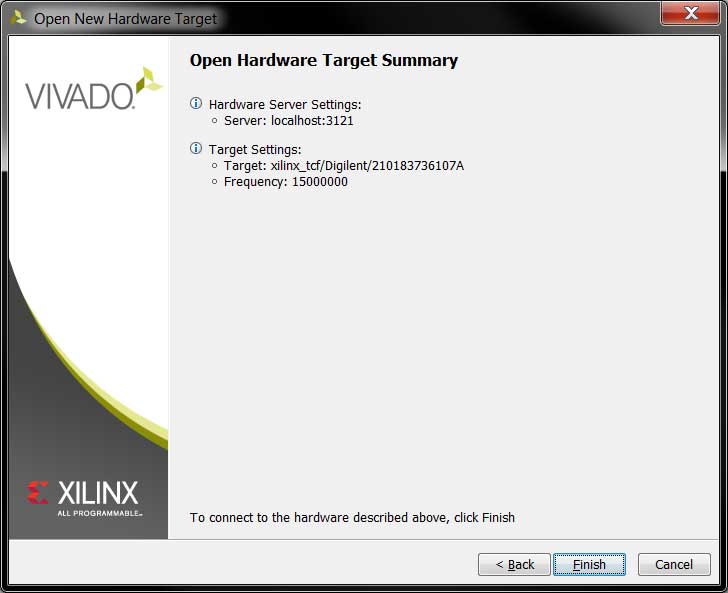

دکمهی “Finish” را بزنید تا Vivado به دستگاه مشخص شدهی شما متصل شود.

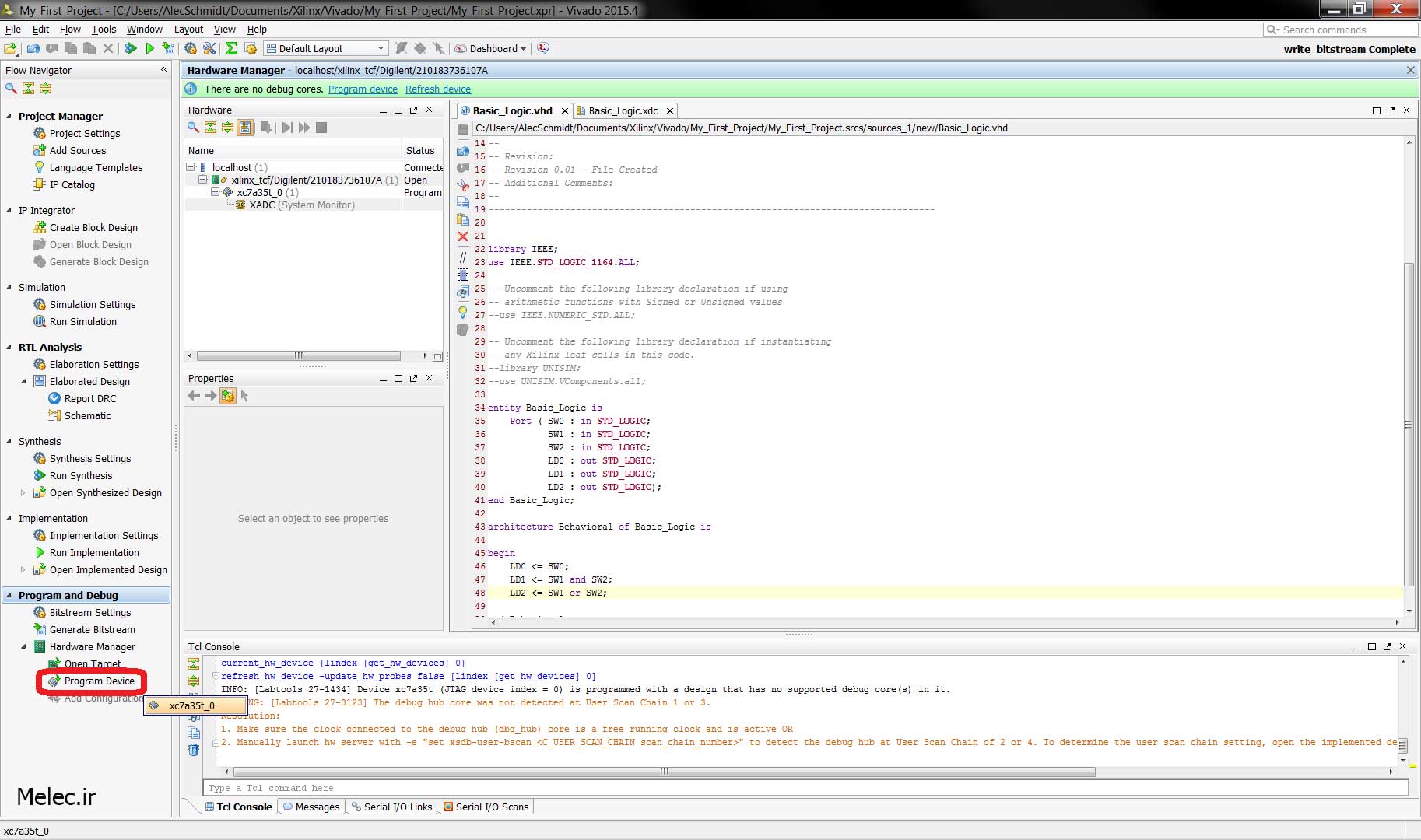

پروگرام کردن دستگاه

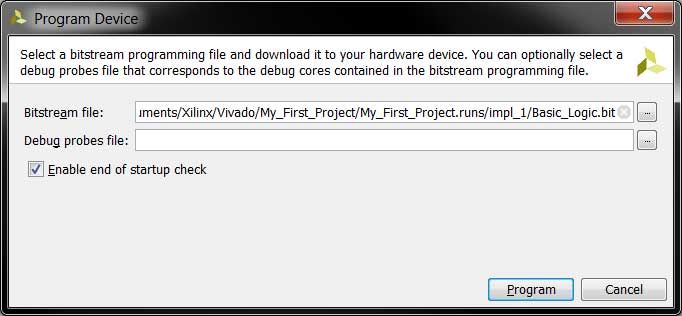

اکنون در قسمت Program and Debug از Flow Navigator گزینهی “Program Device” را بزنید و سپس در پنجرهای که باز میشود دستگاه موردنظر خود را انتخاب کنید.

پنجرهی “Program Device”ای که باز میشود باید دارای آدرس فایل bitstreamای که شما تولید کردید باشد. چک گزینهی “Enable end of startup check” را در صورت نبودن بزنید و سپس دکمهی “Program” را فشار دهید. Vivado برای مدتی شروع به کار میکند، در صورت موفق بودن، بعد از اتمام همه چیز دستگاه شما پروگرام شده و برای بررسی آماده است.

برای افرادی که با برد Basys 3 پیش میآیند، سوییچهای SW0-SW2 را روشن و خاموش کنید و رفتار صحیح LEDهای LD0-LD2 را بررسی کنید.

منبع آموزش نرم افزار Vivado وبسایت: digikey و وبسایت شرکت xilinx

به پایان آموزش نرم افزار Vivado رسیدیم و امیدواریم مفید واقع شده باشه. اگر علاقمند به یادگیری طراحی سیستم های الکترونیک دیجیتال با FPGA هستید به ترتیب این آموزش ها را بخوانید : مدار منطقی – منطق دیجیتال ، انواع حافظه های پرکاربرد ، آموزش FPGA ، دانلود فایل های آموزش FPGA و همچنین اگر در سطح حرفه ای کار میکنید حتما مقاله ZYNQ چیست و چه کاربردی دارد؟ را هم بخوانید.

اگر این نوشته برایتان مفید بود لطفا کامنت بنویسید.

آموزش طراحی و ساخت پروژه های الکترونیک و برنامه نویسی میکروکنترلر ها آموزش الکترونیک,آموزش رزبری پای,آموزش راه اندازی ماژول و سنسور,آموزش آردوینو,نرم افزار های الکترونیک, طراحیPCB,برنامه نویسی میکروکنترلرها ARM AVR PIC FPGA

آموزش طراحی و ساخت پروژه های الکترونیک و برنامه نویسی میکروکنترلر ها آموزش الکترونیک,آموزش رزبری پای,آموزش راه اندازی ماژول و سنسور,آموزش آردوینو,نرم افزار های الکترونیک, طراحیPCB,برنامه نویسی میکروکنترلرها ARM AVR PIC FPGA