خب در ادامهی آموزشهای FPGA به آموزش VHDL میپردازیم. در این جلسه موضوع مورد بحث ما مفاهیم ساده و پیشرفتهی VHDL است. بنابراین هم افراد مبتدی میتوانند از آن استفاده کنند و قدم به قدم با آن پیش بروند و هم افرادی که خود پیشینهای قبلی دربارهی این مفاهیم دارند اما علاقهمند هستند که اطلاعاتشان را تکمیل کننند. عناوینی که به ترتیب بررسی میکنیم از این قرار هستند.

- HDL چیست؟

- VHDL چیست؟

- Verilog چیست؟

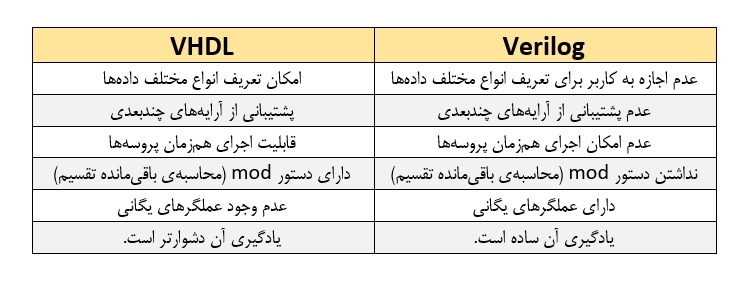

- تفاوتهای VHDL و Verilog چیست؟

- تاریخچهی VHDL

- چرا باید از VHDL استفاده کنیم؟

- مزایای VHDL

- معایب VHDL

- المانهای پایهای زبان VHDL

- انواع روشهای مدلسازی در VHDL

- VHDL آبجکتها (Objects)

- انواع دادهها در VHDL

- انواع عملگرها در VHDL

- آموزش نصب Xilinx IDE

- ایجاد یک پروژهی VHDL با استفاده از Xilinx IDE

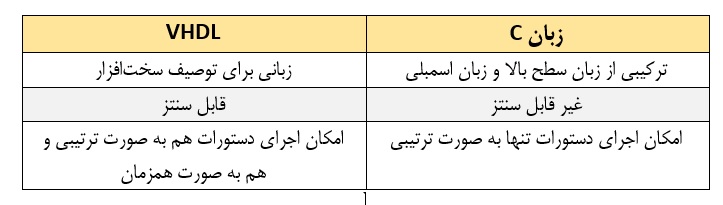

- مقایسهی VHDL با زبان C

پیشنیازهای مفید آموزش VHDL

قبل از یادگیری VHDL اگر علاقمند بودید مطالب زیر میتونن براتون مفید واقع بشن.

HDL چیست؟

HDL خلاصهشدهی عبارت Hardware Description Language به معنای زبان توصیف سختافزار است. به طور دقیقتر؛ HDL زبانی است که از آن برای توصیف، سیمولیشن و ساخت ورژن سختافزاری از مدارهای دیجیتال (ICS) استفاده میشود.

البته عمدهترین کاربرد آن در مرحلهی قبل از پیادهسازی سختافزاری و در یافتن خطاهای طراحیهای انجام شده است. مهمترین مزیتش نیز در این است که قابلیتهای مدلسازی بسیار منعطفی دارد و میتوان با استفاده از آن حتی طراحیهای فوق پیچیده (مثلا بالای 107 گیت) را نیز توصیف کرد.

امروزه، HDLهای مختلفی در بازار عرضه میشوند اما محبوبترین زبانهای توصیف سختافزار VHDL و Verilog هستند.

VHDL چیست؟

VHDL برگرفته از عبارت Very High-Speed Integration Circuit HDL؛ به معنای زبان توصیف سختافزاری برای ICهای سرعت بالا است. این زبان توسط IEEE (موسسه بینالمللی مهندسی برق و الکترونیک) استاندارد شده است و از آن برای شبیهسازی رفتار مدارهای دیجیتالی پیچیده استفاده میشود.

اگر بخواهیم به چند نمونه از مشهورترین کدهای پرکاربرد که با کمک زبان VHDL نوشته شدهاند اشاره کنیم، میتوانیم مواردی چون Odd Parity Generator ،Pulse Generator ،Priority Encoder ،Behavioral Model for 16 words ،8bit RAM را نام ببریم.

زبان VHDL از ویژگیهای زیر برخوردار است.

- انواع متدهای طراحی و ویژگیهای آن

- طراحی رخداد وقایع به صورت ترتیبی و یا همزمان

- امکان تبادل طراحی با نرمافزارهای مختلف

- استانداردسازی

- مستندسازی

- خوانایی زبان طراحی

- طراحی در مقیاس گسترده (Large scale)

- قابلیتهای وسیع در توصیف مدارها

Verilog چیست؟

وریلاگ هم یک زبان توصیف سختافزاری (HDL) دیگر است که از آن در توصیف مدارها و سیستمهای الکترونیکی استفاده میشود. این زبان هم در سیمولیشن و هم در سنتز کاربرد دارد. از مثالهای پرکاربرد آن میتوان سوییچهای شبکه، میکروپروسسورها، حافظهها، فلیپ فلاپها و … را نام برد.

- آموزش مرتبط مفید: آموزش FPGA و Verilog برای تازه کارها!

تفاوتهای VHDL و Verilog

تاریخچهی VHDL

VHDL نخستین بار در سال 1980 و توسط وزارت دفاع آمریکا معرفی شد و توسعه پیدا کرد.

- سال 1980: وزارت دفاع تصمیم گرفت برای طراحی مدارها یک روش خود-استناد (self-documentig) ایجاد کند.

- سال 1983: زبانVHDL با همکاری مشترک سه شرکت IBM ،Texas Instruments و Intermetrics توسعه پیدا کرد.

- سال 1985 (VHDL v 7.2): در قراردادی با دولت، نسخهی نهایی چیزی که توسعه یافته بود عرضه شد.

- سال 1987: وزارت دفاع اجازه داد که از VHDL در مقاصد تجاری نیز استفاده شود و به این ترتیب این زبان برای نخستین بار استاندارد IEEE دریافت کرد. (1076-1987)

- سال 1993: پس از بازنگریها به منظور رفع اشکالات و بهبود، نسخهی به روزتری از VHDL استاندارد سازی شد.

- سال 1996: پکیجی از ابزارهای سنتز مدار با زبان VHDL استاندارد 1076 IEEE مطرح شد.

- سال 1999: اضافه شدن افزونهی VHDL-AMS به آن.

- سال 2008: استاندارد IEEE 1076-2008 با به روزترین تغییرات و اضافه شدن ویژگیهایی جدید، به زبان VHDL اختصاص یافت.

چرا باید از VHDL استفاده کنیم؟

از VHDL برای موارد زیر استفاده میکنیم.

- برای توصیف سختافزاری

- به عنوان یک زبان برای مدلسازی

- برای شبیهسازی سختافزاری

- برای ارزیابیهای اولیه از معماری یک سیستم

- برای سنتز سختافزارها

مزایای VHDL

لیستی از مزیتهای این زبان را در اینجا با هم مرور میکنیم.

- این زبان از متدهای مختلف طراحی مثلا روش Top-down یا Bottom-up یا … پشتیبانی میکند.

- در توصیف سختافزارها زبانی بسیار منعطف است.

- موجب میشود مدیریت یک طراحی بهتر انجام شود.

- امکان پیادهسازی دقیقتر و جزئیتر را فراهم میکند.

- باعث میشود درکی چند لایه از مدار داشته باشیم.

- موجب میشود میان سطوح پایین طراحی با سطوح بالاتر همبستگی معناداری ایجاد شود.

- با تمام ابزارهای CAD سازگار است.

- میتوان کدهای آن را در ابزارهای دیگر به اشتراک گذاشت و از کدهای دیگر در آن استفاده کرد.

معایب VHDL

برخی از معایب زبان VHDL از این قرار هستند.

- برای کار کردن با آن حتما باید سینتکسها و ساختارهای مخصوص به این زبان را یاد بگیرید.

- تجسم و در نتیجه عیبیابی مدارها قدری در آن پیچیدهتر است.

- برخی از برنامههایی که به زبان VHDL نوشته میشوند قابل سنتز نیستند.

- یادگیری آن کمی مشکل است.

المانهای پایهای زبان VHDL

زبان VHDL دارای سه جزء تشکیل دهندهی اساسی است.

1. Entity

منظور از entity در این زبان، پورتهای ورودی و خروجی یک مدار است. هر entity معمولا دارای یک یا تعداد بیشتری پورت است که میتوانند ورودی (in)، خروجی (out)، ورودی-خروجی (inout) و یا بافر باشند.

البته در مواردی نیز منظور از entity میتواند مجموعهای از مقادیر و پارامترهای عمومی باشد که برای تعیین مشخصات مدار به کار میروند.

چگونگی تعریف Entity

برای مشخص کردن اینکه یک entity چیست، میتوان از سینتکس زیر استفاده نمود.

- روش سینتکس ساده شده

entity entity_name is

ort (

port_1_name : mode data_type;

ort_2_name : mode data_type;

.......

Port_n_name : mode data_type

);

end entity_name;مثال:

entiy orgate is

port (

a : in std_logic;

b : in std_logic;

c : out std_logic

);

end orgate;- روش تعریف پارامترهای عمومی (generics)

اگر قرار باشد یک entity مشخص کنندهی genericها باشد، باید این موضوع حتما قبل از مشخص کردن پورتها قید بشود. ضمنا genericها دارای مود به خصوصی نیستند و تنها میتوانند اطلاعات را به entity منتقل کنند.

سینتکس:

entity entity_name is

generic (

generic_1_name : data_type;

generic_2_name : data_type;

........

generic_n_name : data_type

);

port (

port_1_name : mode data_type;

port_2_name : mode data_type;

........

Port_n_name : mode data_type

);

end entity_name;مثال:

entity Logic_Gates is

generic (Delay : Time := 10ns);

port (

Input1 : in std_logic;

Input2 : in std_logic;

Output : out std_logic

);

end Logic_Gates;قوانینی برای نامگذاری پورتها:

- نام پورتها میتواند شامل حروف الفبا، اعداد و آندرلاین ( _ ) باشد.

- همیشه باید با یک حرف الفبا شروع بشود.

- بزرگ یا کوچک بودن حروف استفاده شده، نامها را از هم متمایز نمیکند.

مودهای مختلفی که پورتها میتوانند داشته باشند:

- In: پورت ورودی

- Out: پورت خروجی

- Inout: پورت دوطرفه

- Buffer: پورت خروجی بافر شده

2. معماری

معماری قسمت اصلی توصیف یک طراحی است. یعنی توضیح اینکه یک مدار چگونه قرار است کار کند. این معماری میتواند هم شامل توصیف انجام کارها به صورت ترتیبی (sequential) باشد و هم انجام کارها به صورت همزمان (concurrent).

چگونگی تعریف معماری

این کار را میتوان با استفاده از سینتکسی به صورت زیر انجام داد.

architecture architecture_name of entity_name is

begin

(concurrent statements )

end architecture_name;مثال:

architecture synthesis of andgate is

begin

c <= a AND b;

end synthesis;3. پیکربندی

در بخش کانفیگوریشن (configuration) مشخص میکنیم که قسمتهای مختلف یک طراحی چگونه با هم ارتباط پیدا میکنند. همچنین چگونگی ارتباطات میان بخش معماری و قسمت entityها را نیز در اینجا تعریف میکنیم.

چگونگی تعریف کانفیگها

configuration configuration_name of entity_name is

--configuration declarations

for architecture_name

for instance_label : component_name

use entity library_name.entity_name(architecture_name);

end for;

--

end for;

end [configuration] [configuration_name];مثال:

configuration demo_config of even_detector_testbench is

for tb_archi

for uut : even_detector

use entity work.even_detector (sop_archi);

end for;

end for;

end demo_config;انواع روشهای مدلسازی در VHDL

در VHDL برای مدل کردن معماریها چهار روش داریم.

-

مدلسازی با روش جریان داده (طراحی معادلات)

در این روش مدل سازی را براساس عبارتهای بولین انجام میدهند و به کمک این عبارتها نشان میدهند روالی که دادهها برای رسیدن از ورودی به خروجی طی میکنند به چه صورت است. این روش برای معماریهای اجرا همزمان (Concurrent) قابل استفاده است.

-

مدلسازی به روش رفتاری (behavioral)

در این روش تلاش میکنیم سیستم را با توصیف مرحله به مرحلهی رفتار آن مدل کنیم. یعنی به صورت ترتیبی و سلسلهوار (sequential) تعریف میکنیم که هر بار چه عبارتهایی اجرا میشوند. به این ترتیب رفتار کلی سیستم بر اساس این جملات و ترتیب اجرای آنها مشخص میشود.

عبارتها و جملاتی که در این روش استفاده میشوند، میتوانند شامل عبارتهای پردازشی (Process statements)، ترتیب اجرای عملیات (Sequential statements)، تخصیص سیگنال (Signal assignment) و یا کنترلی (wait statements) باشند.

-

مدلسازی به روش ساختاری (استفاده از زیرماژولها (sub-modules) و اتصال دادن آنها به هم)

این روش مدلسازی برای توصیف ساختار یک مدار و کاربرد آن استفاده میشود. این روش شامل تعریف سیگنالها (signal declarations)، نمونهگیری از تمام اجزا مدار (component instances) و تعیین نقشهی پورتها (port map) در هرکدام از این نمونههاست.

VHDL آبجکتها

در زبان VHDL ما سه نوع آبجکت داریم.

-

ثابتها

آبجکتهای که تنها میتوانند یک مقدار را بپذیرند و این مقدار در تمام طول برنامه تغییر نمیکند.

مثال:

constant number_of_bytes integer:=8;

-

متغیرها

این آبجکتها نیز تنها یک مقدار را میپذیرند اما تفاوت آنها با آبجکتهای ثابت، در این است که این مقدار میتواند در طول اجرا یا شبیهسازی برنامه از طریق اپراتورهای تخصیص مقدار (assignment operator) تغییر داده شود. از متغیرها میتوانیم در زیربرنامهها و پردازشها استفاده کنیم و برای تخصیص دادن هر مقداری که باید به آنها داده شود؛ از اپراتور «=:» استفاده میکنیم.

مثال:

variable index: integer :=0;

-

سیگنالها

سیگنالها را میتوان در بخش معماری تعریف کرد و هرکجا که لازم باشد در آن بخش از آنها استفاده کرد. برای اینکه مقداری را به آنها تخصیص بدهیم از اپراتور«=>» استفاده میکنیم.

مثال:

Signal sig1: std_logic;

Sig1 <= ‘1’

انواع دادهها در VHDL

با تعیین نوع داده، در واقع به طور ضمنی میخواهیم مشخص کنیم دادهای که مورد اشارهی ماست از چه جنسی است. به طور کلی میتوان دادهها را در دو نوع کلی جای داد که هر گروه نیز خود دارای انواعی به صورت زیر است.

-

داده های از نوع اسکالر یا عددی

- Integer: این نوع دادهها متعلق به مجموعهی تمام اعداد مثبت یا منفی هستند.

- Floating point: دادههای متعلق به مجموعهی تمام اعداد اعشاری مثبت یا منفی.

- Enumeration: دادههای شمارشی دادههایی هستند که از آنها استفاده میکنیم تا کدهای ما خواناتر شوند.

- Physical: دادههایی که از نوع فیزیکال باشند، معرف آبجکتها براساس واحد پایهی آنها، یا مجموعههایی از واحدهای پایه و یا محدودههایی مشخص هستند.

-

دادههای مرکب یا کامپوزیت

- آرایهها (Arrays): از آرایهها استفاده میکنیم تا تعدادی متغیر از یک نوع را در کنار هم و با یک شناسه تعریف و ذخیره کنیم.

- Record: از نوع دادهی رکورد برای مشخص کردن یک یا تعداد بیشتری المان که هرکدام نام و نوع متفاوتی دارد، استفاده میکنیم.

انواع عملگرها در VHDL

برای ساختن عبارتهای توصیفی از عملگرها استفاده میکنیم. عملگرهای زبان VHDL در چهار دسته قابل طبقهبندی هستند.

-

عملگرهای منطقی

عملگرهایی برای کنترل جریان برنامه. اگر این عملگرها را در کنار سیگنالها یا متغیرها استفاده کنیم؛ آنگاه منطق ترکیبی (combinational logic) خواهیم داشت. عملگرهای منطقی زبان VHDL عبارات زیر هستند.

And, or, nand, Nor, xor, xnor, Not

-

عملگرهای مقایسهای

از عملگرهای مقایسهای برای مقایسه میان دو متغیر که از یک نوع داده هستند استفاده میشود. خروجی و نتیجهی این عملگرها همواره از نوع بولین است. عملگرهای مقایسه ای زبان VHDL را در زیر مشاهده میکنید.

| برابری |

= Equal to |

| نابرابری |

/= Not Equal to |

| کوچکتر بودن |

< Less than |

| بزرگتر بودن |

> Greater than |

| کوچکتر یا مساوی بودن |

<= Less than or equal to |

| بزرگتر یا مساوی بودن |

>= Greater than or equal to |

-

عملگرهای ریاضیاتی

این عملگرها همانطور که از نام آنها برمیآید برای انجام دادن عملیاتهای ریاضیاتی مورد استفاده قرار میگیرند. متغیرهایی که میتوانند این عملگرها را بپذیرند طبیعتا باید از نوع شمارشی باشد. عملگرهای ریاضیاتی که VHDL از آنها پشتیبانی میکند را مشاهده میکنید.

| جمع |

+ Addition |

| تفریق |

– Subtraction |

| ضرب |

* Multiplication |

| تقسیم |

/ Division |

| الحاق کردن |

& Concatenation |

| محاسبهی باقیماندهی تقسیم (با قاعدهی همنهشتی) |

mod Modulus |

| محاسبهی باقیماندهی تقسیم (با روش معمولی) |

rem Remainder |

| محاسبهی قدر مطلق اعداد |

abs Absolute Value |

| توان رسانی |

** Exponentiation |

-

عملگرهای جابهجایی یا انتقال

در زبان VHDL، عملگرهای شیفت یا جابهجایی را برای مدیریت و جابهجایی بیتها به کار میبرند. به این ترتیب که به اندازهی گفته شده بیتهای آن عملوند را به راست یا چپ جابهجا کرده یا میچرخانند. انواع مختلف عملگرهای انتقالی که در VHDL قابل استفاده هستند شامل این موارد هستند.

| شیفت منطقی به چپ |

Sll: shift logical left |

| شیفت منطقی به راست |

Srl: shift logical right |

| شیفت ریاضیاتی به چپ |

Sla: shift arithmetic left |

| شیفت ریاضیاتی به راست |

Sra :shift arithmetic right |

| چرخاندن بیتها یک واحد به سمت چپ |

Rol: rotate left |

| چرخاندن بیتها یک واحد به سمت راست |

Ror: rotate right |

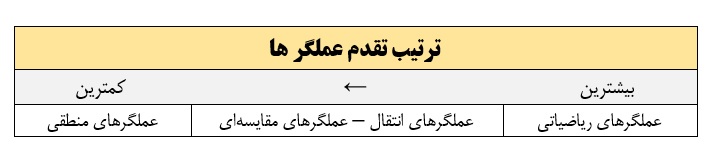

نکته: اگر در عبارتی چند نوع عملگر از گروههای مختلف وجود داشته باشد، ترتیب اعمال شدن آنها براساس اولویتهای قراردادی تعیین شده است. از پر اولویتترین به کم اولویتترین.

عملگرهایی که تقدم و اولویت برابر دارند، ترتیب اعمال آنها از چپ به راست است.

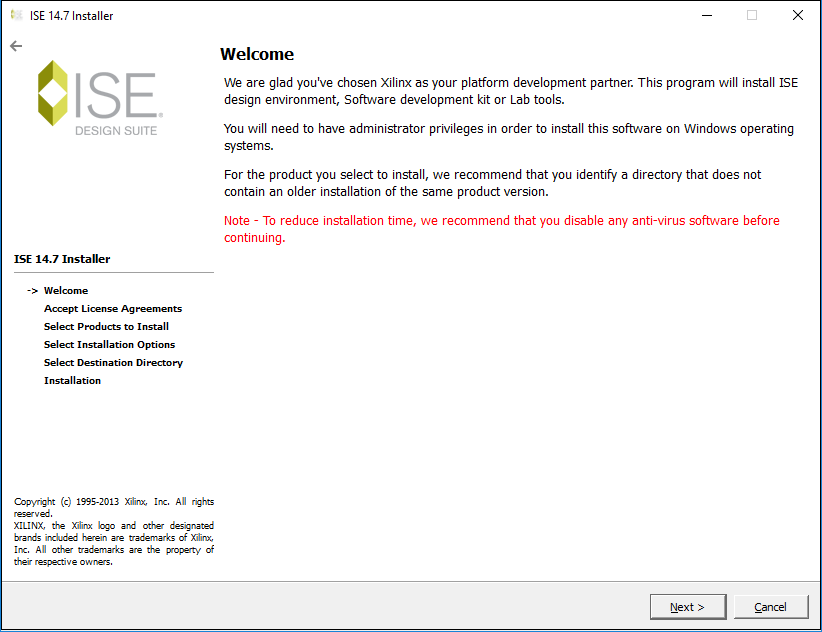

آموزش نصب Xilinx IDE

برای نصب Xilinx ISE باید مراحل زیر را قدم به قدم طی کنیم.

مرحله اول

بر روی لینک زیر کلیک کنید تا Xilinx ISE tool دانلود شود.

نکه مهم: شما میتوانید به جای Xilinx ISE از Xilinx Vivado هم برای نوشتن کدهای VHDL استفاده کنید. مقاله آموزش نرم افزار Vivado را در این راستا مطالعه کنید.

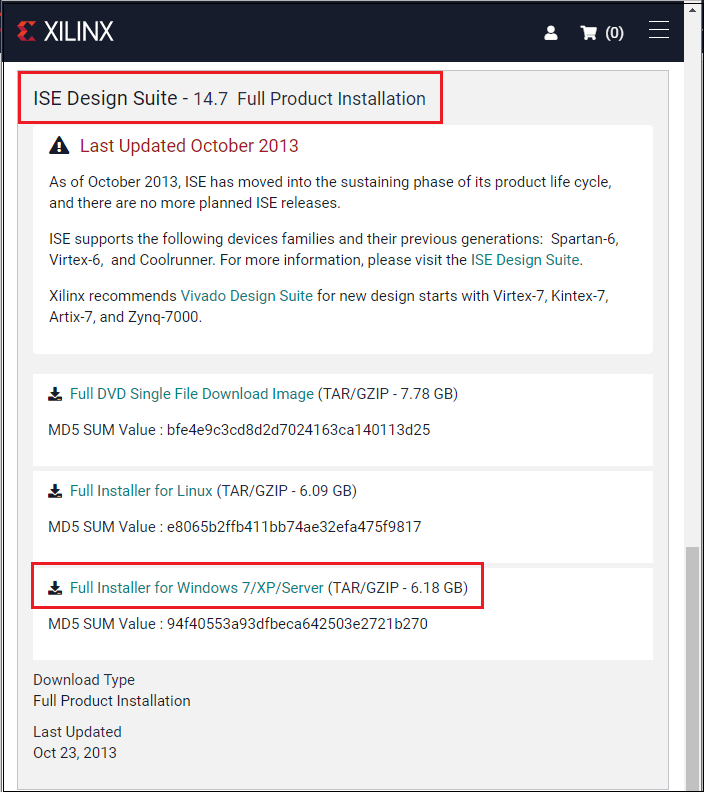

مرحله دوم

پس از دانلود به ISE Design suite – 14.7 Full Product Installation بروید و از آنجا مانند تصویر زیر سومین گزینه یعنی Full Installer for Windows 7/XP server (TAR/GRIP – 6.18 GB) را بزنید.

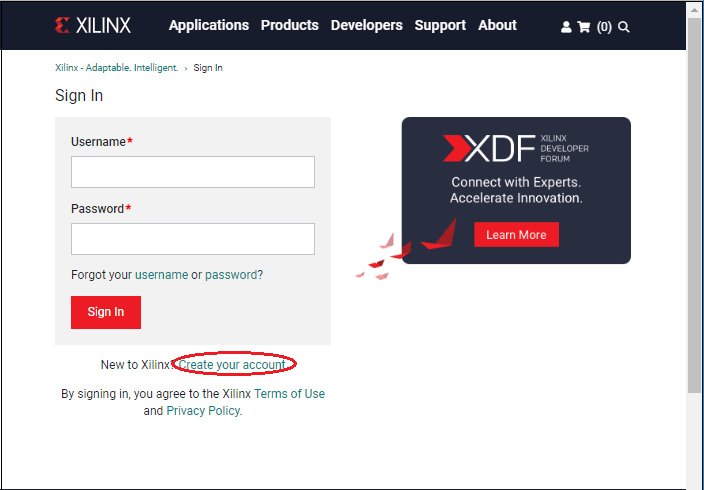

مرحله سوم

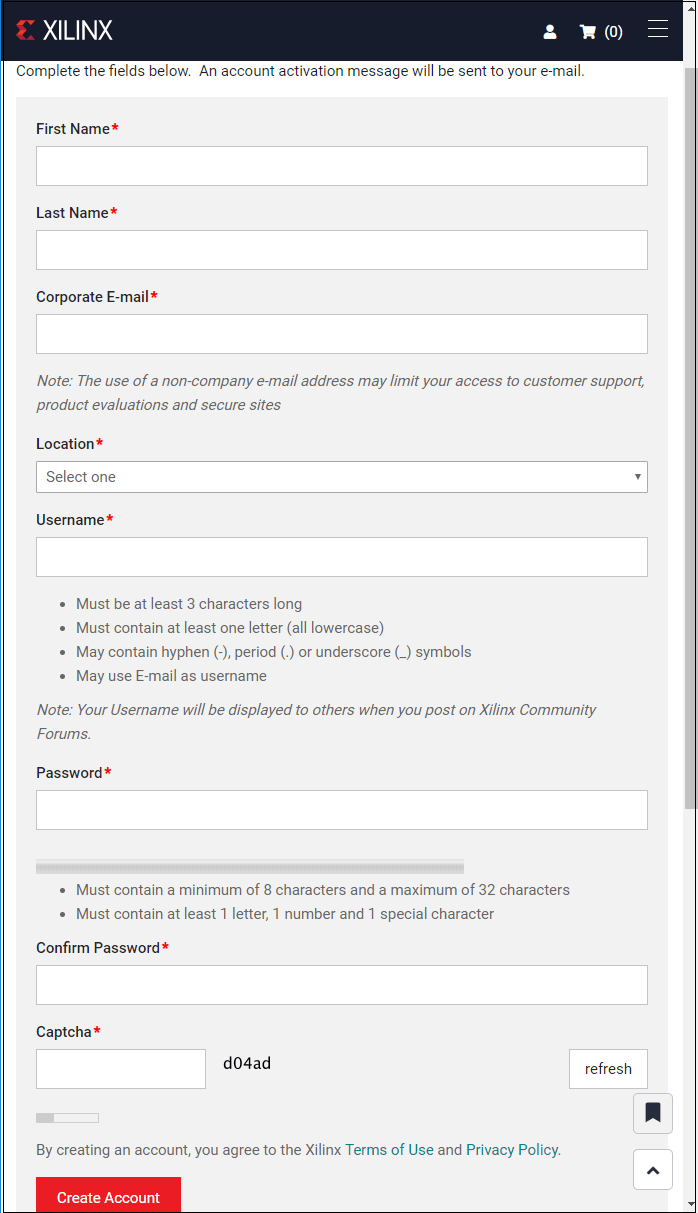

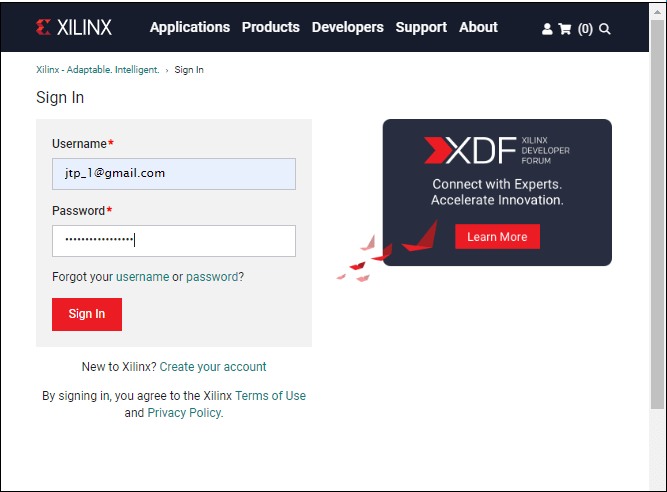

پس از کلیک بر روی گزینهی فوق، یک صفحهی sign in یا ورود برای شما باز میشود. اگر از قبل یک اکانت زایلینکس ندارید، بر روی گزینهی ساخت اکانت جدید کلیک کنید.

مرحله چهارم

در صفحهی ثبت نام، اطلاعات خواسته شده را وارد کنید و گزینهی ایجاد حساب را بزنید.

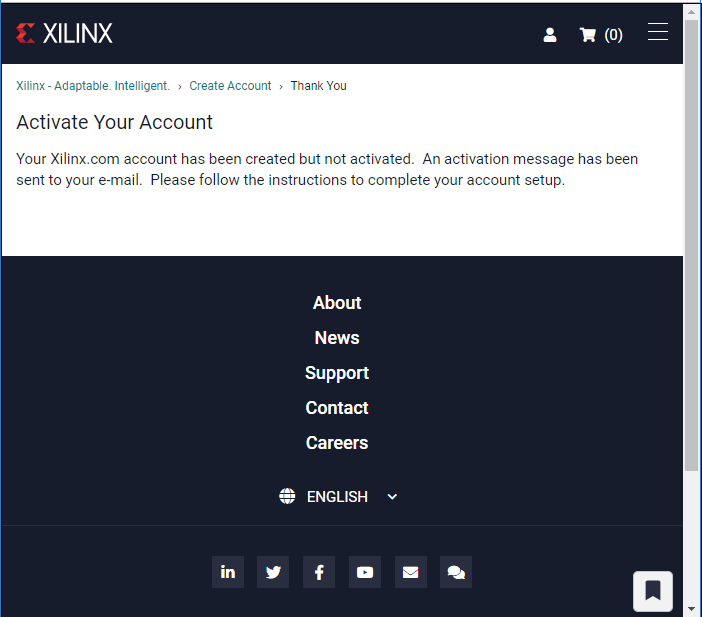

مرحله پنجم

پس از آنکه Create Account را زدید، پنجرهای مانند تصویر زیر باز خواهد شد.

مرحله ششم

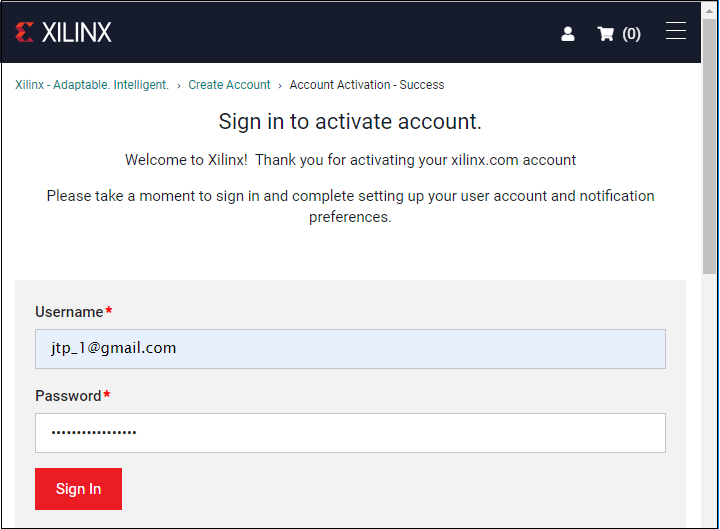

در این مرحله شما باید به ایمیلی که در زمان ثبت اطلاعات وارد کردهاید بروید و ایمیلی که برایتان ارسال شده و حاوی لینک فعالسازی حساب است را باز کنید. پس از دریافت و باز کردن ایمیل، بر روی لینک فعالسازی کلیک کنید.

مرحله هفتم

با کلیک بر روی لینک، پنجرهای برای فعالسازی حساب باز خواهد شد. در آنجا باید username و password را بزنید و وارد شوید.

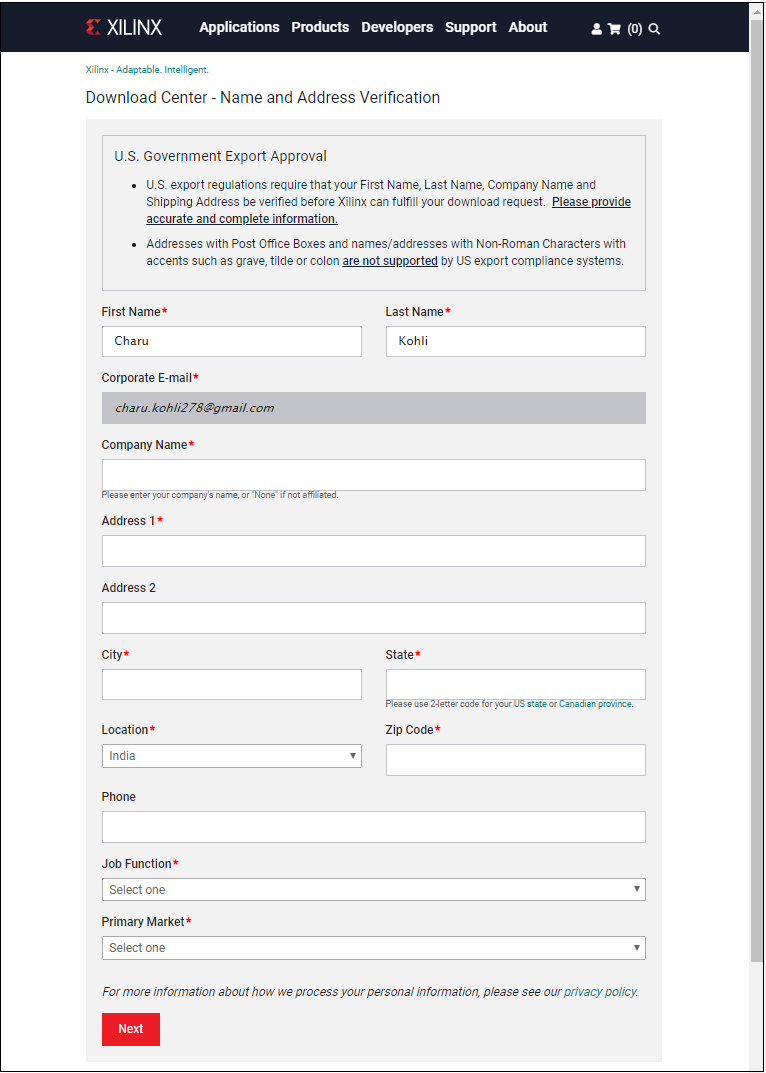

مرحله هشتم

حالا برای تایید نام و آدرس، بر روی لینک زیر کلیک کنید.

https://www.xilinx.com/member/forms/download/xef.html?filename=Xilinx_ISE_DS_Win_14.7_1015_1.tar

مرحله نهم

پس از تایید فرم verification، با زدن next به مرحله بعدی بروید.

مرحله دهم

در این مرحله میبینید که فایل Xilinx_ISE tar شروع به دانلود شدن میکند.

![]()

مرحله یازدهم

هنگامی که دانلود شد آن را از حالت فشرده خارج کنید.

مرحله دوازدهم

پس از اجرای برنامه، پنجرهی خوشآمدگویی را مانند تصویر زیر در مقابلتان خواهید دید.

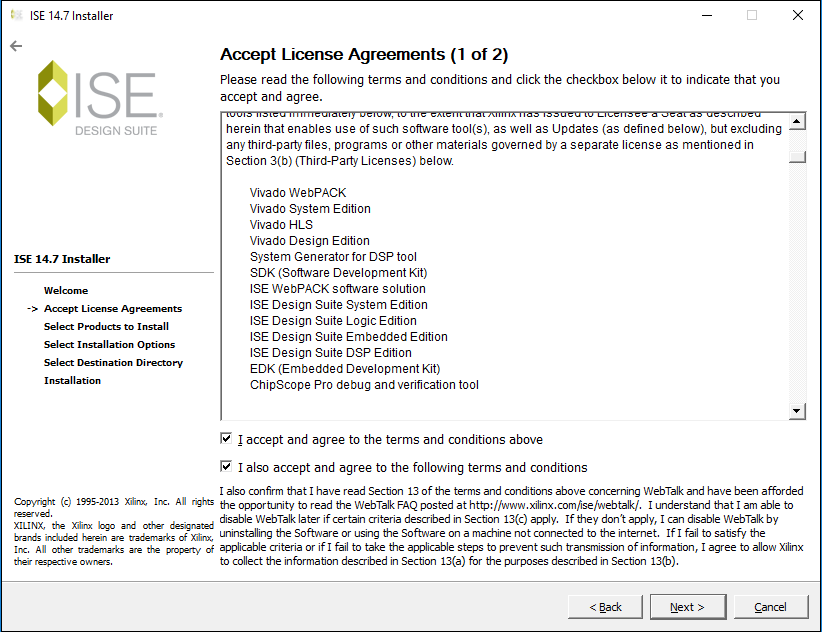

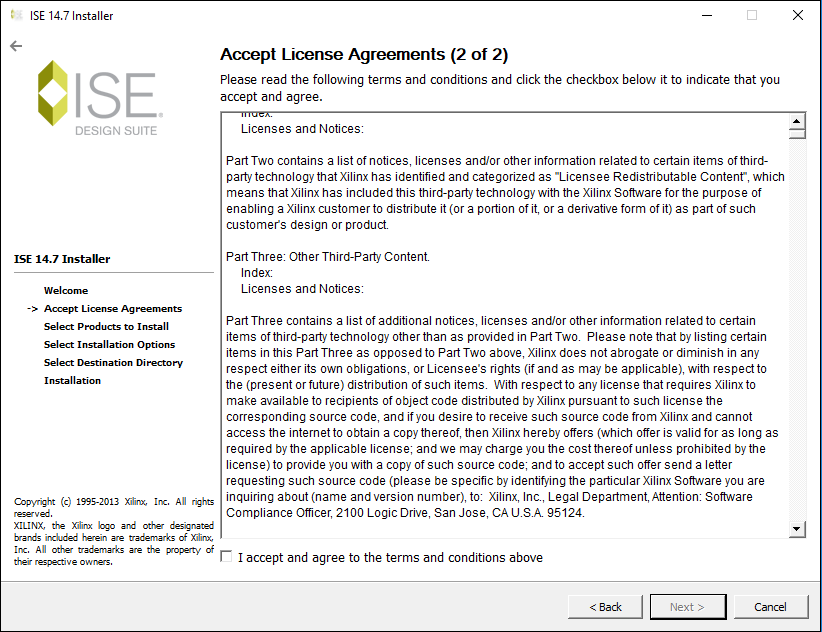

مرحله سیزدهم

تیک گزینههای موافقت و قبول شرایط را بزنید و به مراحل بعدی بروید.

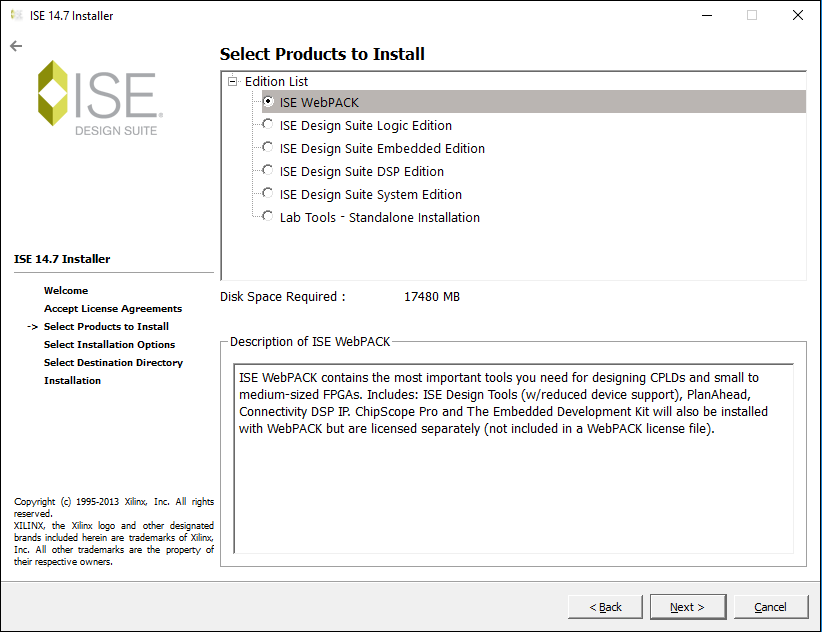

مرحله چهاردهم

خب حالا باید از لیستی که وجود دارد، محصولی که میخواهید نصب شود را انتخاب کنید. برای VHDL، گزینهی ISE WebPACK را که نسخهی رایگان نرمافزاری است انتخاب کنید. پس از زدن تیک انتخاب، به مرحلهی بعدی بروید.

مرحله پانزدهم

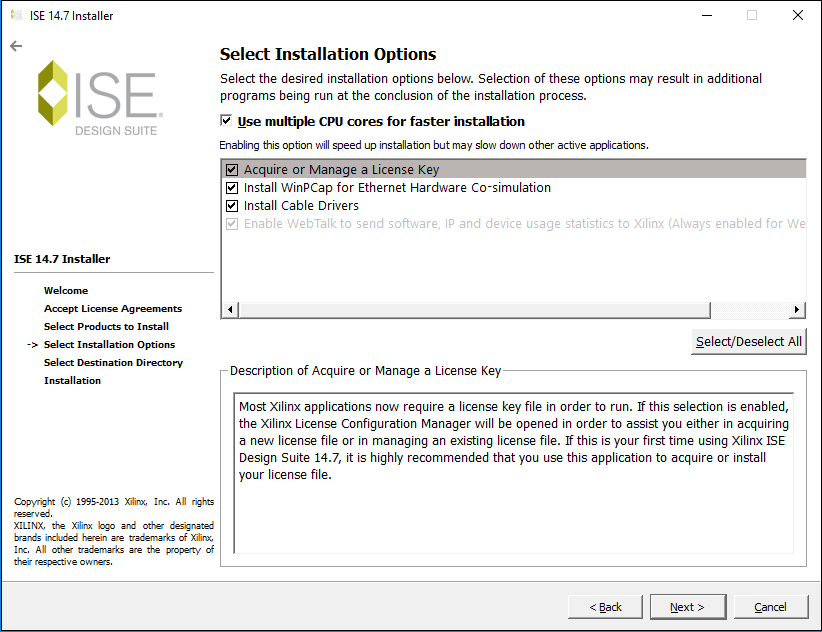

در پنجرهی بعدی که آپشنهای مختلف نصب را نشان میدهد، next را بزنید و به مرحله بعدی بروید.

مرحله شانزدهم

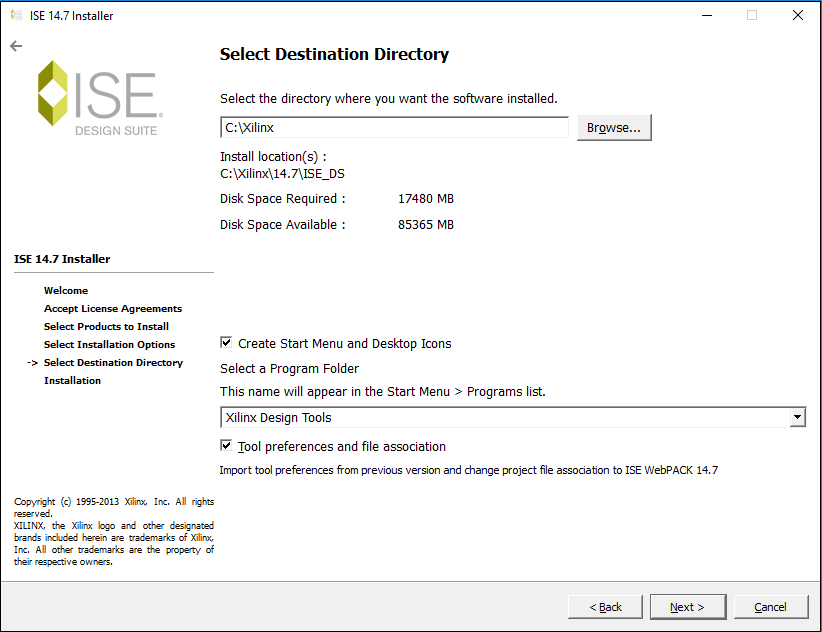

دایرکتوری مقصد برای نصب برنامه را انتخاب کنید و به مرحله بعدی بروید.

مرحله هفدهم

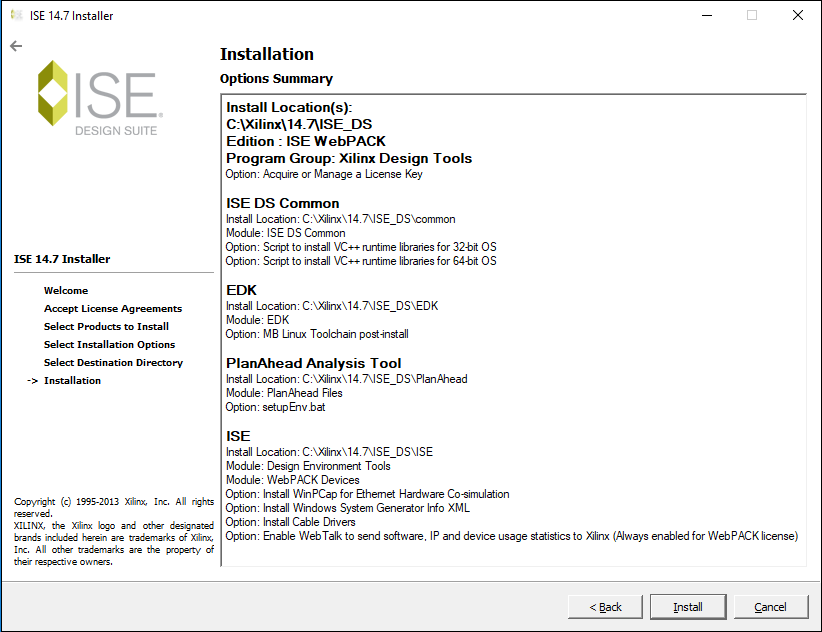

در پنجرهی بعدی، مانند تصویر زیر خلاصهای از شرایط نصب که انتخاب کردهاید را میبینید. گزینهی install را بزنید تا فرآیند نصب شروع شود.

مرحله هجدهم

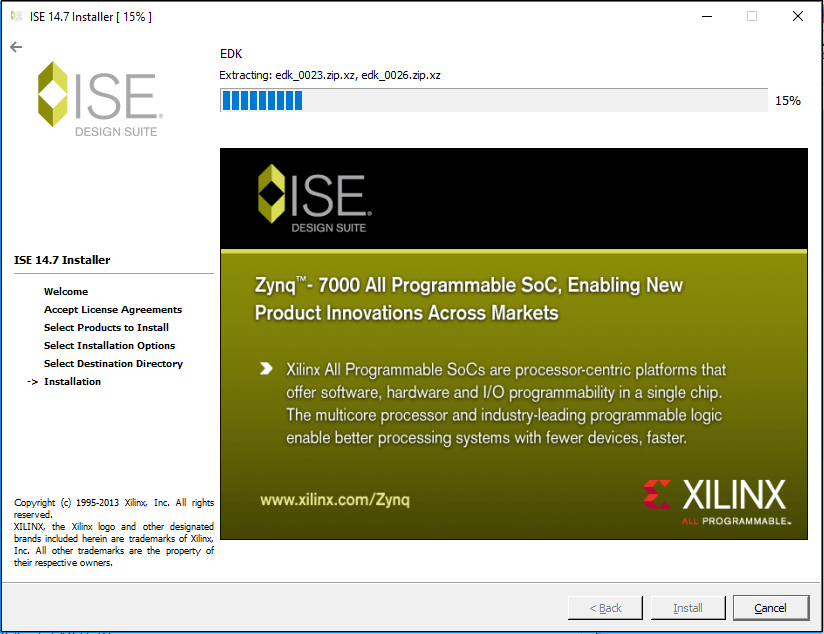

میبینید که فرآیند نصب در جریان است.

مرحله نوزدهم

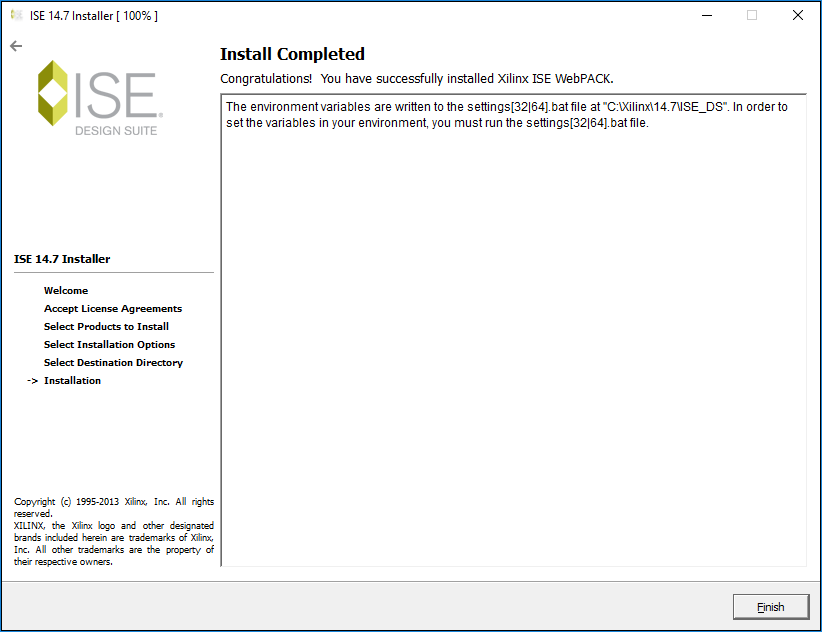

زمانی که فرآیند به پایان رسید و گزینه finish ظاهر شد، آن را بزنید.

مرحله بیستم

در این مرحله باید Project Navigator ،iMPACT و License Manager را تنظیم کنیم.

برای این کار باید مراحل زیر را به ترتیب انجام دهیم.

- به مسیر C:\Xilinx\14.7\ISE_DS\ISE\lib\nt64 بروید و در آنجا فایل dll را پیدا کنید و نام آن را به lib.Portability.dll.orig تغییر دهید.

- فایل dll را هم در همان آدرس کپی کنید و نام آن را به libPortability.dll تغییر دهید.

- dll را در مسیر C:\Xilinx\14.7\ISE_DS\common\lib\nt64 کپی کنید.

- به مسیر C:\Xilinx\14.7\ISE_DS\common\lib\nt64 بروید و در آنجا فایل dll را به libPortability.dll.orig تغییر نام دهید.

- به مسیر C:\Xilinx\14.7\ISE_DS\common\lib\nt64 بروید و در آنجا فایل dll را به libPortability.dll تغییر نام دهید.

پس از انجام دادن دستورات فوق، مسیر باز شده را ببندید و به ادامهی مراحل قبلی بازگردید.

مرحله بیستویکم

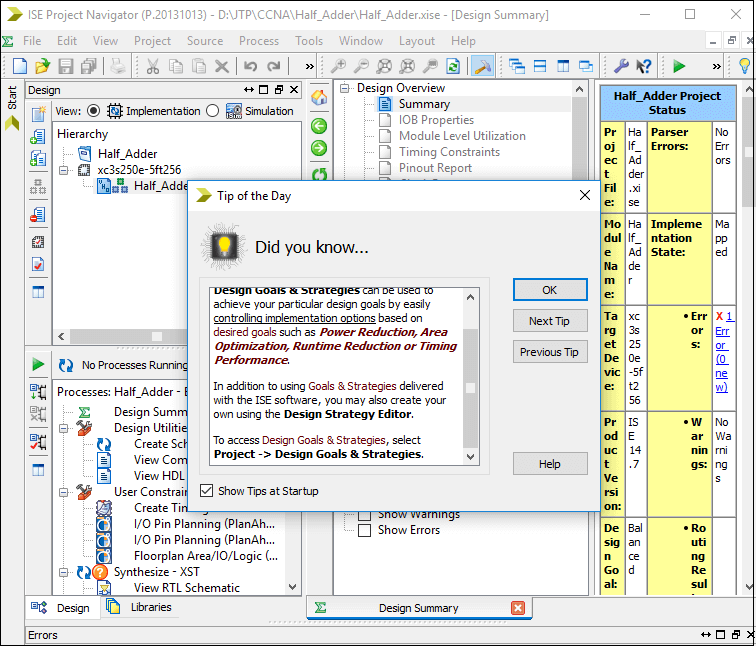

حالا میتوانید ببینید که آیکون IDE Design Suite روی صفحه ظاهر میشود. اگر بر روی آن دبل کلیک کنید، پنجرهی زیر باز خواهد شد.

مرحله بیستودوم

پس از آن پنجرههای زیر در مقابل شما خواهند بود. در پنجرهی pop-up، اکی را بزنید تا بسته شود.

مرحله بیستوسوم

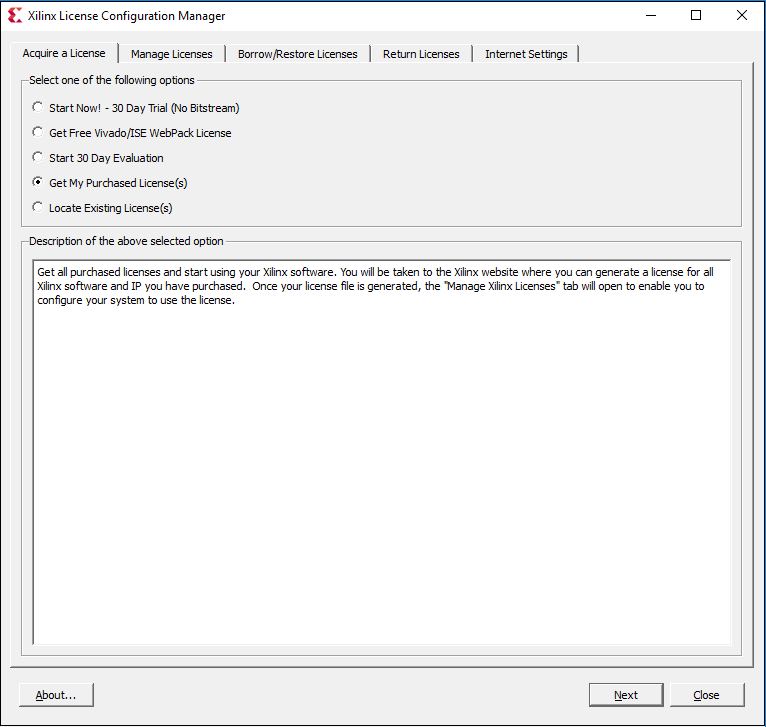

زمانی که بر روی Licence کلیک میکنید، پنجرهای مانند تصویر زیر باز خواهد شد که در آن باید گزینهی Get My Purchased Licence (s) را انتخاب کنید و به مرحلهی بعد بروید.

مرحله بیستوچهارم

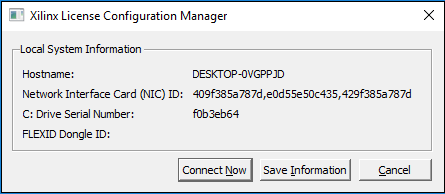

برای آنکه به جستجوگر پیشفرض متصل شوید، Connect Now را بزنید.

مرحله بیستوپنجم

یک صفحهی XILINX جدید باز میشود که در آن باید نام کاربری و پسورد را وارد کنید و sign in را بزنید.

مرحله بیستوششم

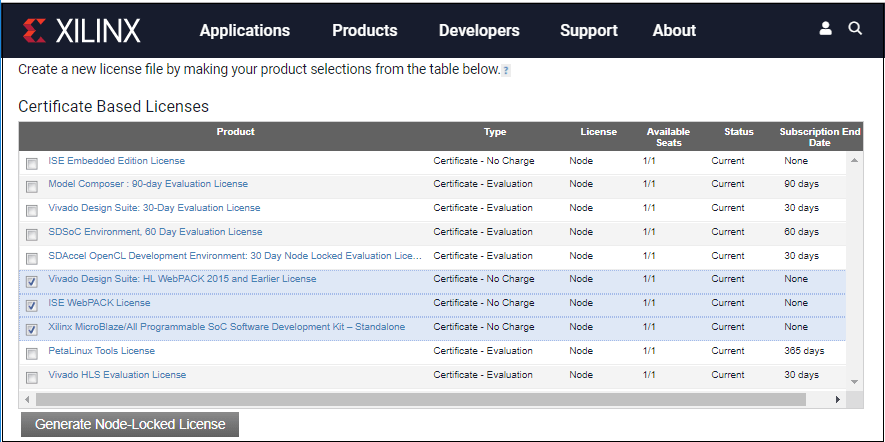

پس از وارد شدن، صفحهای مانند تصویر زیر باز خواهد شد.

مرحله بیستوهفتم

پس از اینکه فایل مد نظر را انتخاب کنید، به همان ایمیلی که در ابتدای ایجاد حساب وارد کرده بودید، یک ایمیل ارسال میشود که محتوی یک فایل Xilinx.lic است. آن را دانلود کنید.

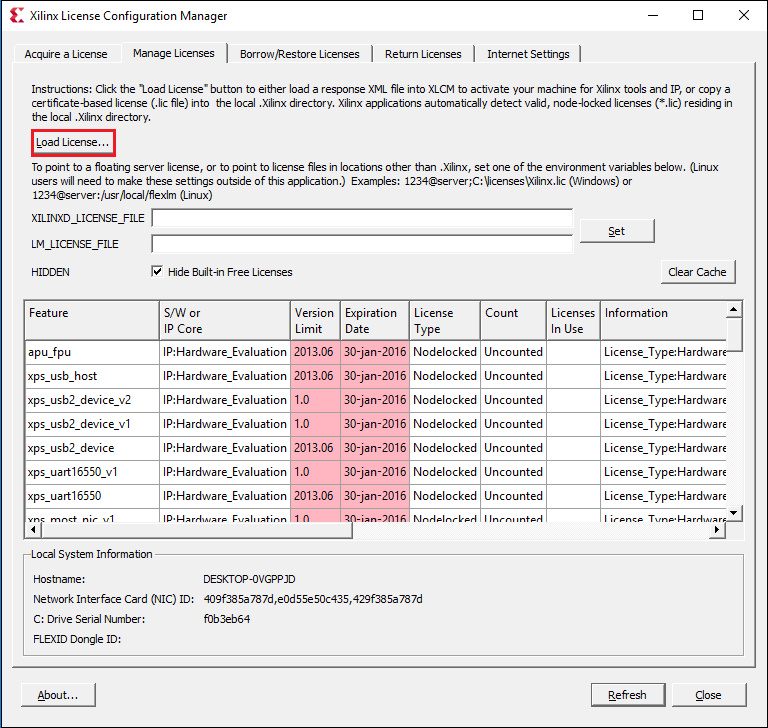

بر روی load Licence کلیک کنید و این فایل لایسنسی که همین حالا دانلود کردید را در اینجا آپلود کنید.

مرحله بیستوهشتم

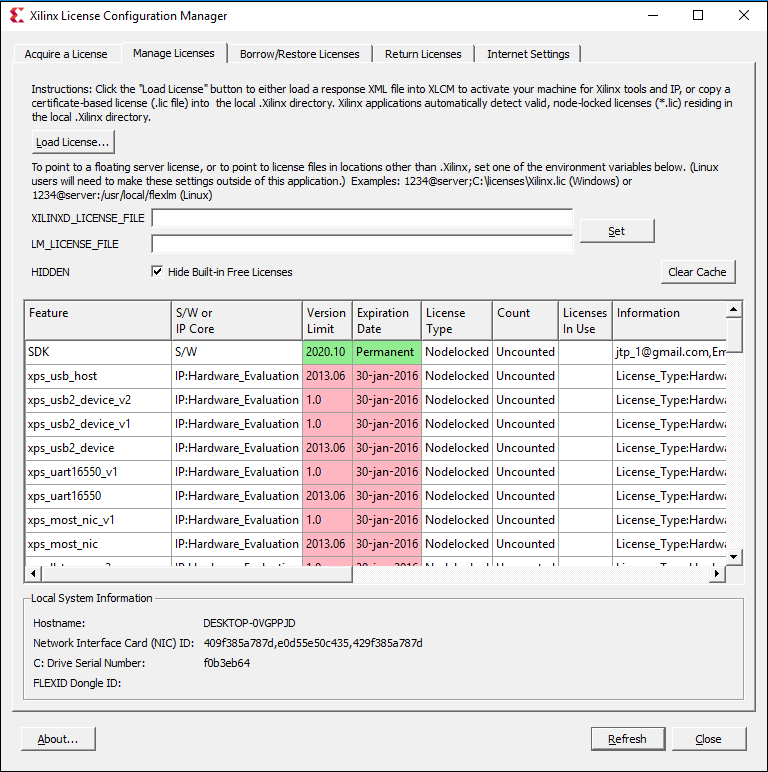

زمانی که آپلود شدن تکمیل شد، یک پنجرهی pop-up با پیغام موفقیتآمیز بودن نصب لایسنس باز میشود. در آن پنجره بر روی Ok و سپس بر روی close بزنید.

در تصویر زیر آپلود شدن لایسنس را میبینیم.

مرحله بیستونهم

حالا همه چیز آماده است که بتوانید در Xilinx tool پروژه بسازید.

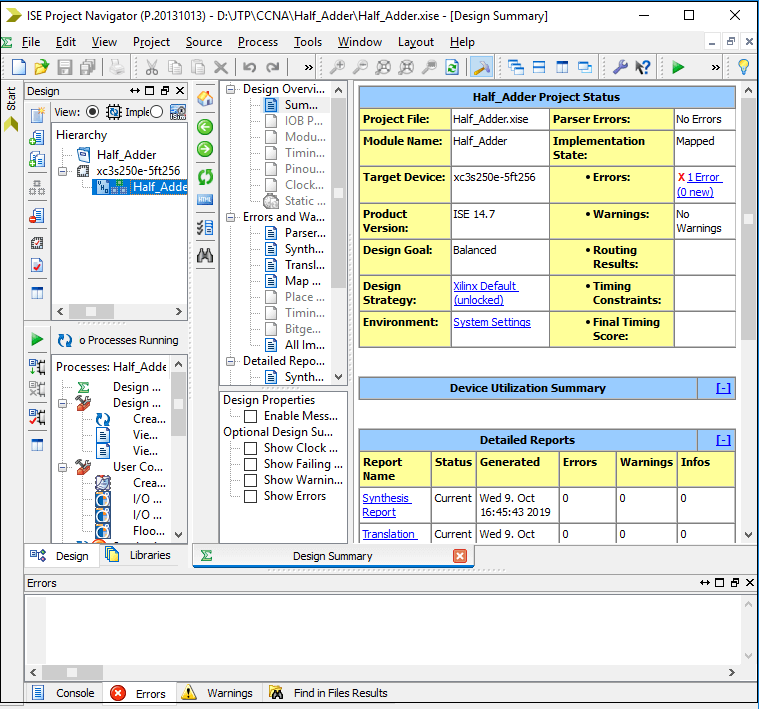

ایجاد یک پروژهی VHDL با استفاده از Xilinx IDE

برای ایجاد یک پروزه در Xilinx IDE، مراحل زیر را به ترتیب انجام میدهیم.

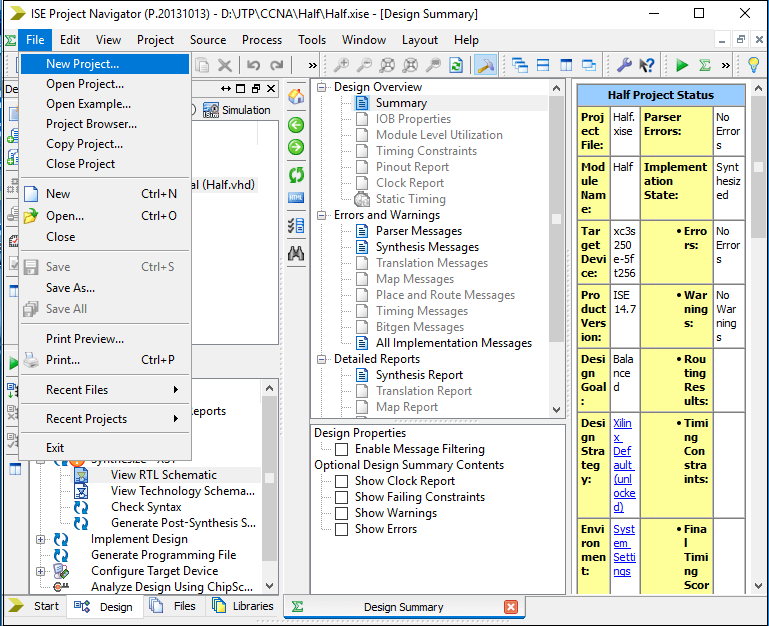

قدم اول: ساخت یک پروژه جدید

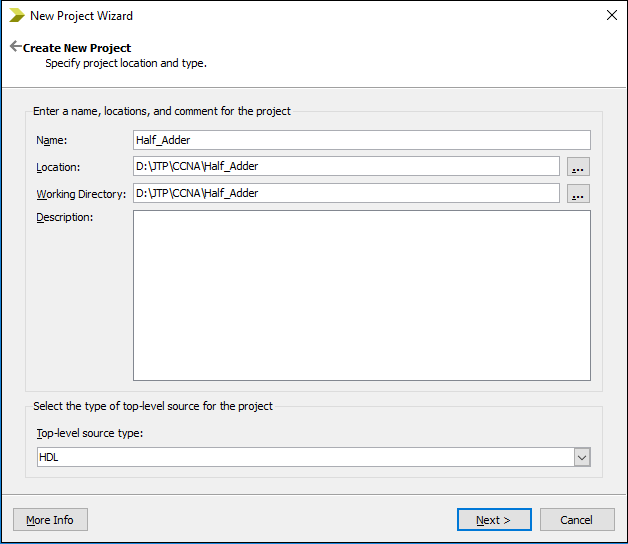

برای این کار به مسیر Select File -> New Project بروید. پس از آن پنجرهی مربوط به یک پروژهی جدید بر روی دسکتاپ باز خواهد شد.

در پنجرهی باز شده، طبق روال آشنای اکثر نرمافزارها، نام پروژه و مسیر ذخیره شدن فایلهای آن را تعیین کنید و پس از آن next را بزنید.

نکته: حتما دقت کنید که Top-level source type را HDL انتخاب کنید و نه شماتیک یا EDIF و یا stuff.

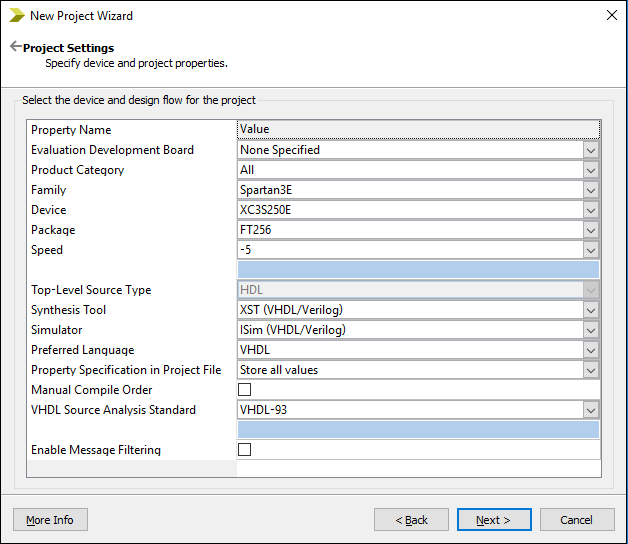

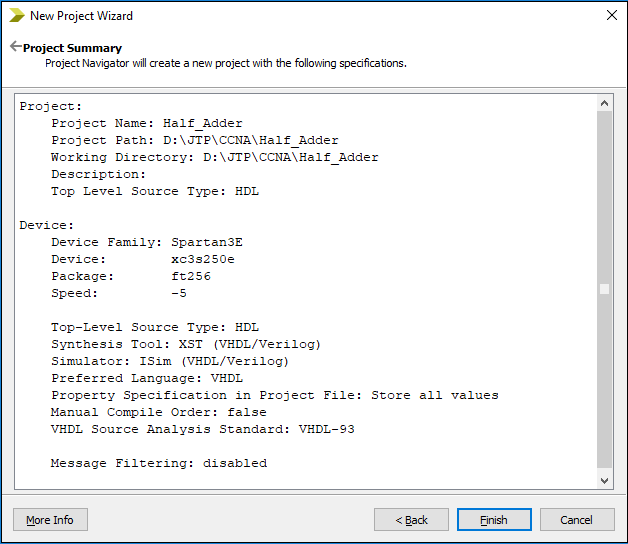

مرحلهی بعدی، مانند تصویر زیر است. ویژگیهای خواسته شده را براساس نیازهای پروژهای که میخواهید بسازید وارد کنید و next را بزنید.

پنجرهی مرحله ی بعدی را در تصویر زیر میتوانید ببینید. همانطور که واضح است خلاصهای از مشخصات تعیین شده برای پروژه را گزارش میدهد. بررسی کنید و ببینید که اگر همه چیز درست انتخاب شده است، finish را بزنید و اگر مغایرتی وجود داشت، به مراحل قبلی بازگردید و مشخصات را مطابق خواسته خودتان تنظیم کنید.

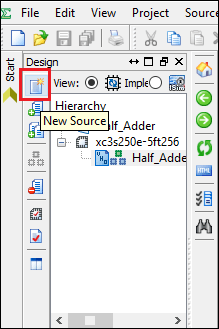

قدم دوم: ساخت یک VHDL source

برای این کار، در project Wizard به قسمت New Source بروید. و یا از این مسیر، Project -> New Source

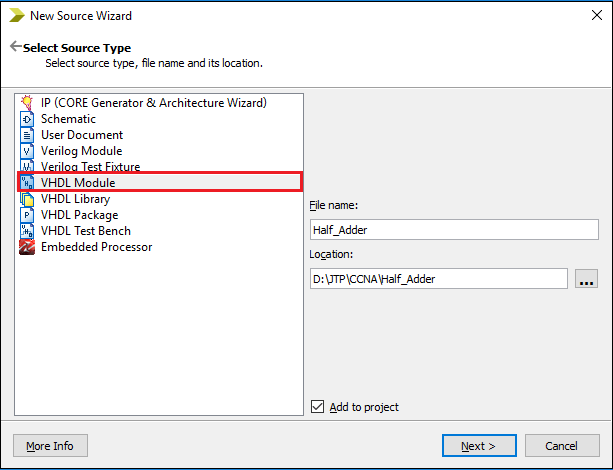

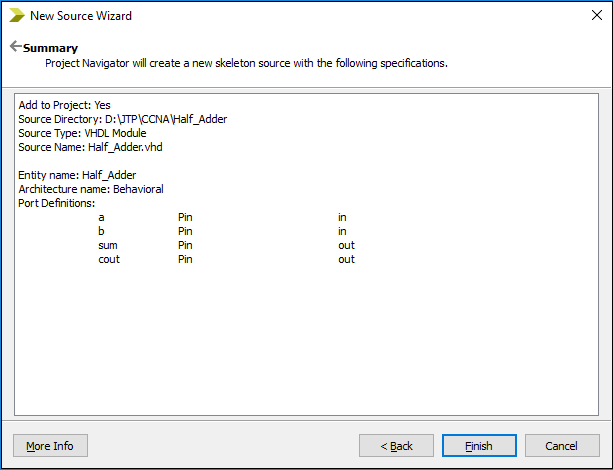

نام فایل را بنویسید و محل آن را مشخص کنید. در قسمت source type هم VHDL Module را بزنید. مطمئن شوید که تیک گزینهی Add to Project را هم زده باشید. سپس به مرحله بعد بروید.

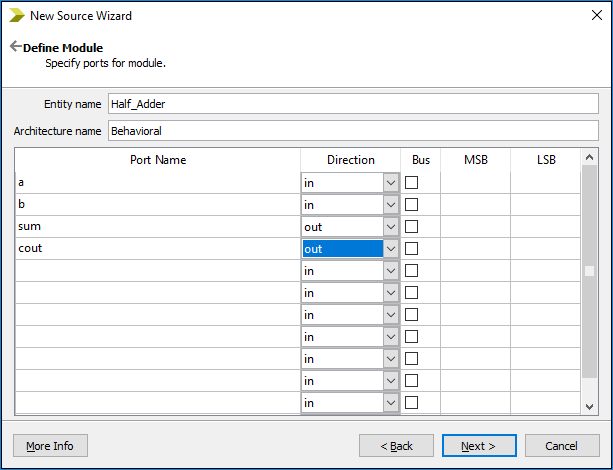

قدم سوم: تعیین پورتهای VHDL source ساخته شده

خب، فرض کنید میخواهیم یک Half Adder بسازیم. پورتهایی که لازم داریم را میتوانیم مانند زیر نامگذاری کنیم.

A, b, sum, cout

که a و b را به عنوان پورتهای ورودی میگیریم. پس از منویی که در روبهروی آنها قرار دارد (مانند تصویر زیر)، گزینهی in به معنای ورودی را انتخاب میکنیم. دو پورت دیگر را هم به عنوان خروجی گرفتهایم پس از منوی مقابلشان گزینه out را میزنیم.

تصویر بعدی خلاصهای از وضعیت پروژه را گزارش میکند.

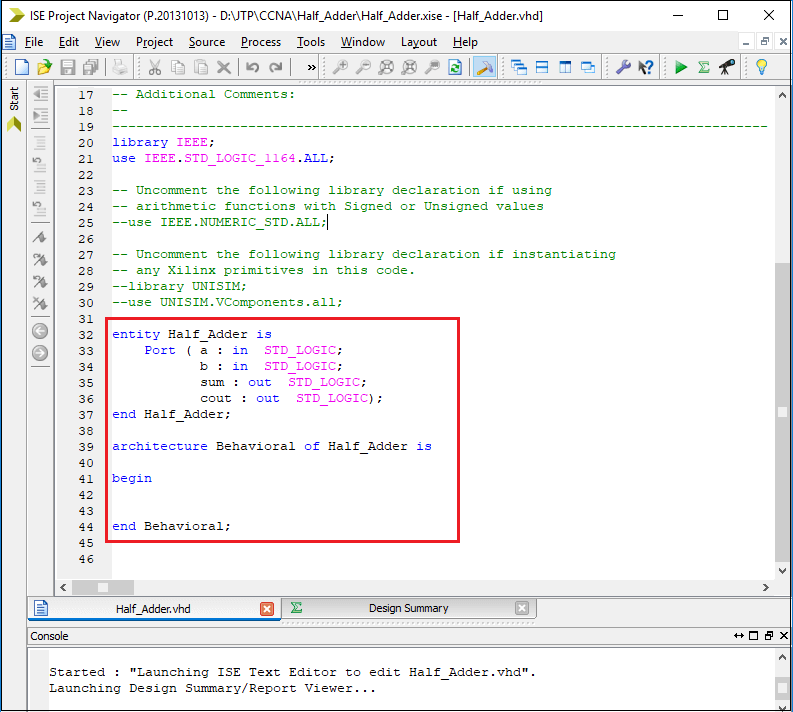

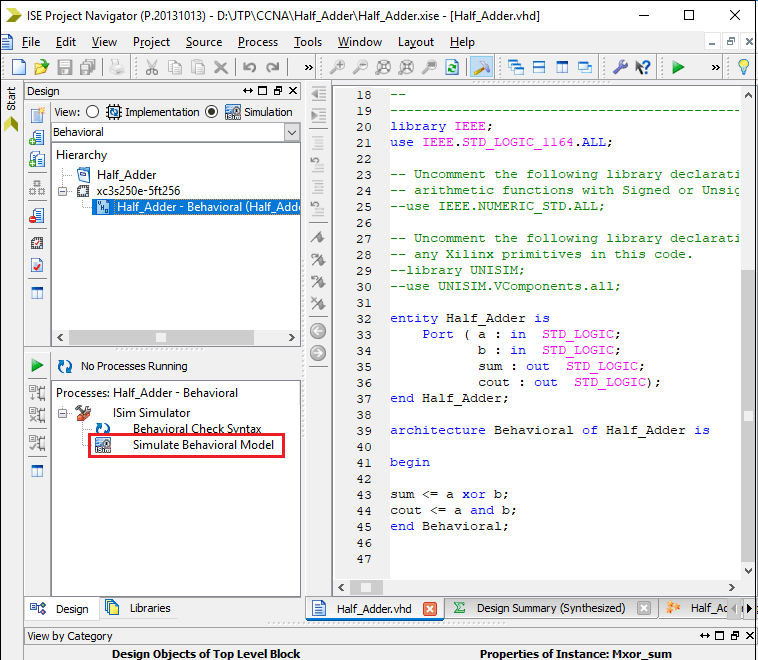

قدم چهارم: وارد کردن یا ویرایش کردن کد VHDL

در تصویر بعدی میبینیم که کد Half Adder به صورت اتوماتیک تولید شده است.

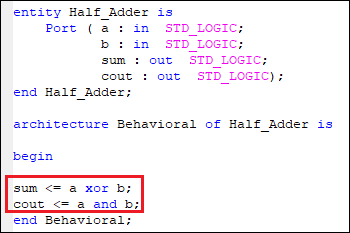

برای تکمیل کد و طراحی مدار، در قسمتی که در تصویر زیر مشخص شده است، کد مشخص شده را وارد کنید.

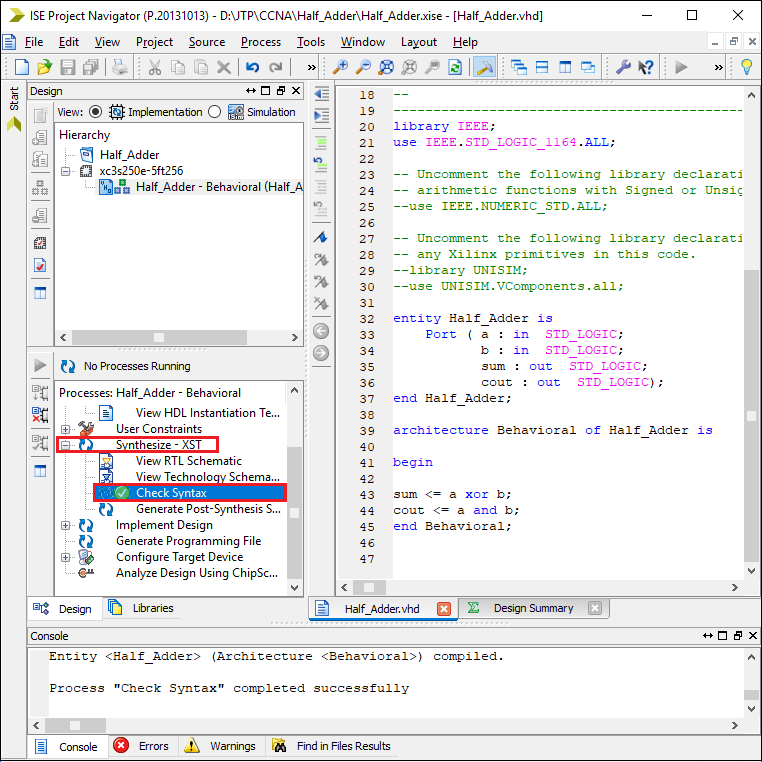

قدم پنجم: سنتز کردن کد

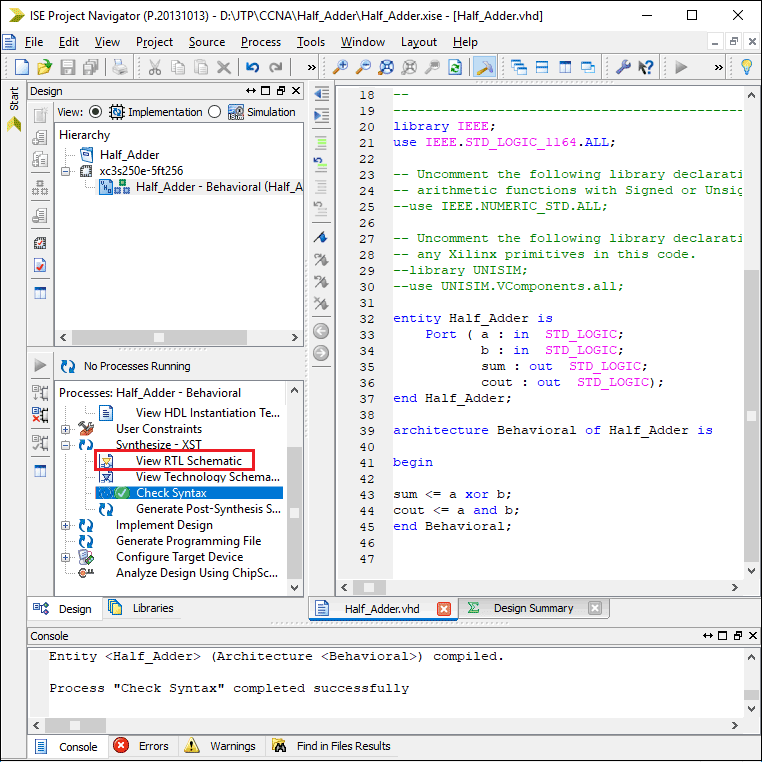

زمانی که فایل سورس شما تکمیل شد، باید سینتکسهای مدار طراحی شده را بررسی کنید. برای این کار باید از فرآیند Synthesize-XST استفاده کنیم. پس بر روی Check syntax دبل کلیک کنید.

پس از آن میبینید که پروسهی کامپایل شدن کد توسط ISE شروع میشود. اگر با موفقیت کامپایل شود یک تیک سبز رنگ در پنجره ظاهر میشود. در غیر این صورت یک ضربدر قرمز رنگ میبینید که نشان میدهد در بخشی از کد احتمالا خطایی وجود دارد.

برای دیدن طراحی اولیهای که پس از کامپایل شدن کد، برای مدار Half adder در نظر گرفته شده است، کافی است بر روی RTL Schematic دبل کلیک کنید.

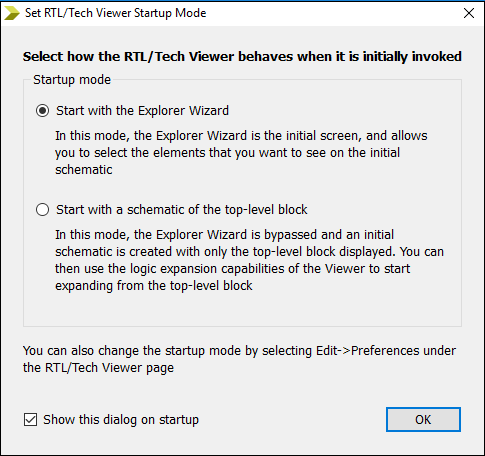

پس از آن پنجرهی زیر باز خواهد شد که باید Ok را بزنید.

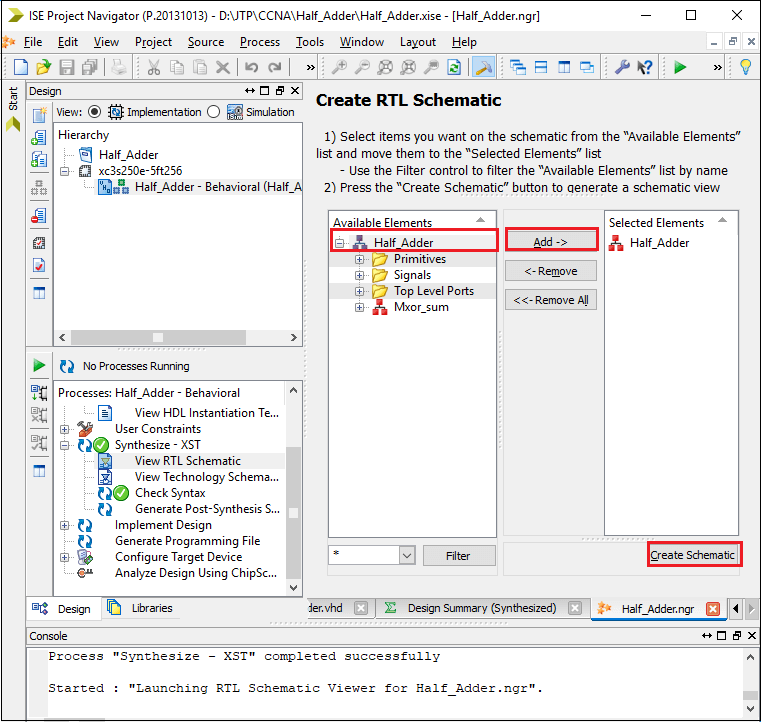

در قسمت create RTL Schematic، پروژهای که میخواهید را از لیست موجود انتخاب کنید. سپس دکمهی Add را بزنید تا از لیست سمت چپ به لیست سمت راست اضافه شود. سپس Create Schematic را بزنید.

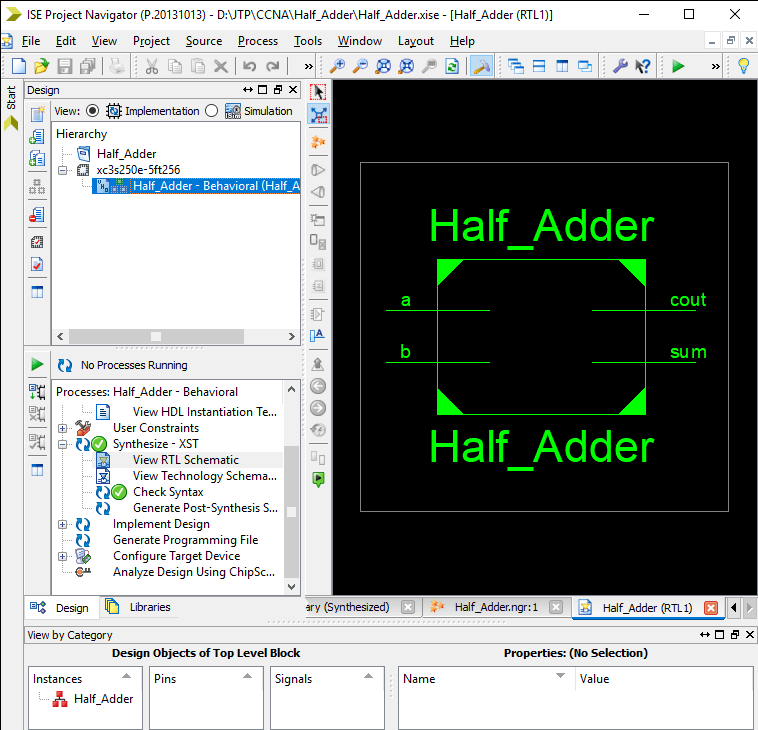

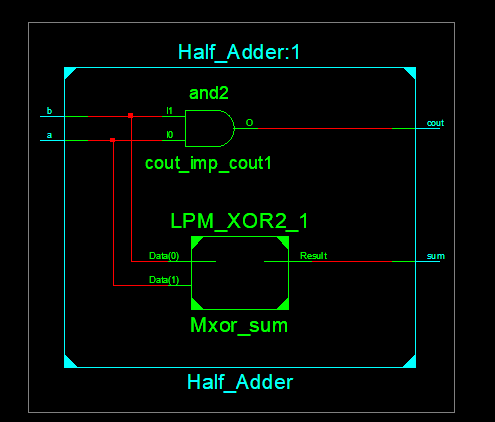

حالا میتوانید طراحی خارجی (بلک باکس) مدار در نظر گرفته شده برای Half adder را ببینید.

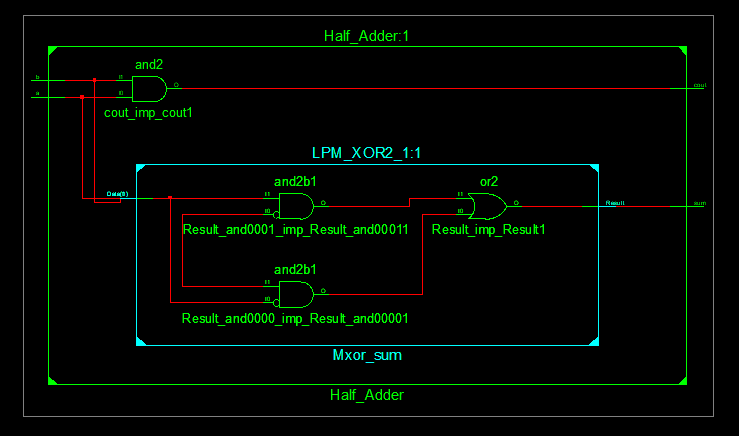

اگر بر روی بلک باکس (قاب مستطیلی شکلی که تنها پورتهای ورودی و خروجی آن مشخص هستند) دبل کلیک کنید، مدار داخلی که متشکل از گیتهای منطقی است نیز به شما نشان داده خواهد شد.

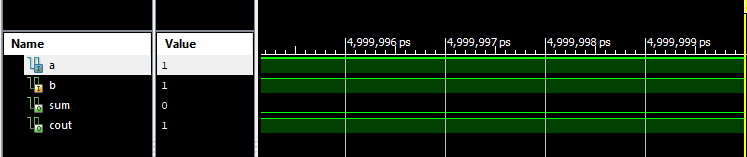

قدم ششم: شبیهسازی یا سیمولیشن مدل رفتاری (ISE Simulator)

برای چک کردن مدل رفتاری مدار نیم-جمعکنندهای که ساختهایم، به مسیر Implementation-> Half_Adder- Behavioral (Half_Adder.vhd) بروید و از آنجا بر روی Simulate Behavioral Model کلیک کنید.

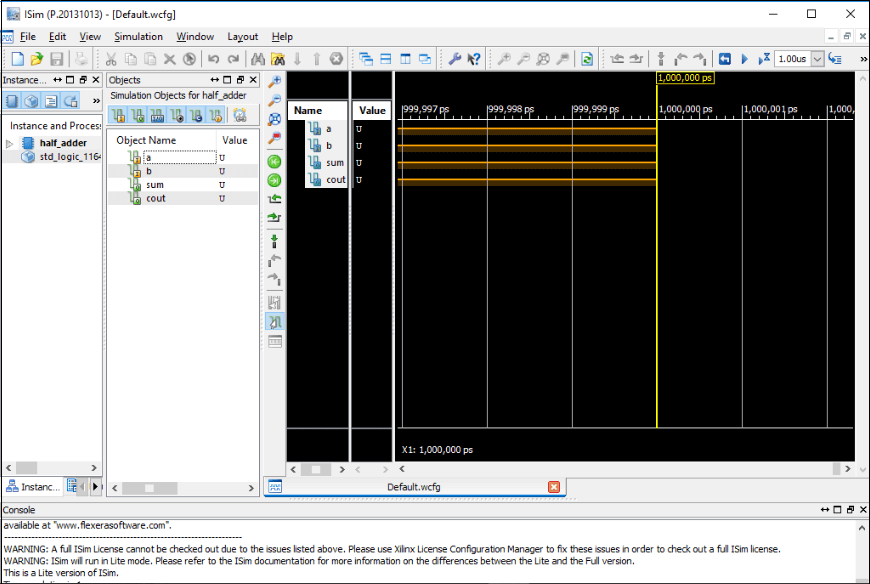

اگر سیمولیشن با موفقیت انجام شود، پنجرهی زیر باز میشود.

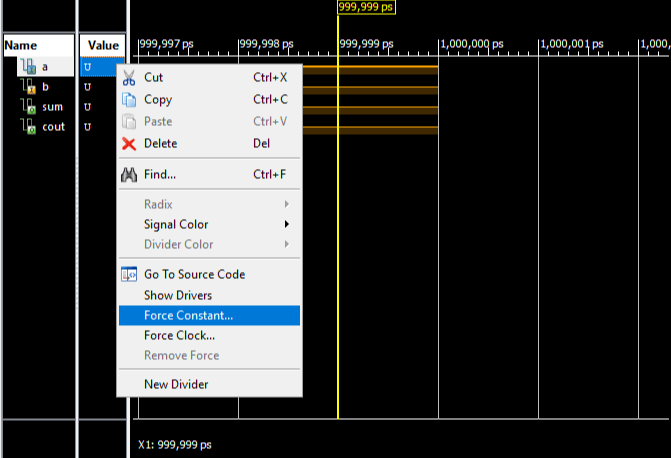

برای مقداردهی به متغیرها، بر روی مقدار فعلی آنها (U) راست کلیک کنید و Force Constant را انتخاب کنید. دقیقا مانند تصویر زیر.

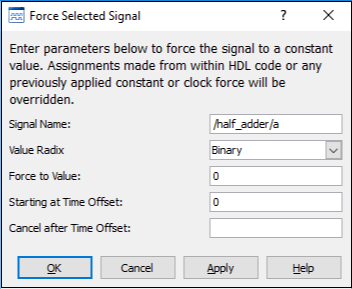

در پنجرهای که مانند تصویر بعدی باز میشود، شما میتوانید مقدار ثابت دلخواه را به متغیر بدهید.

در چند حالت رفتار مدار را بررسی میکنیم.

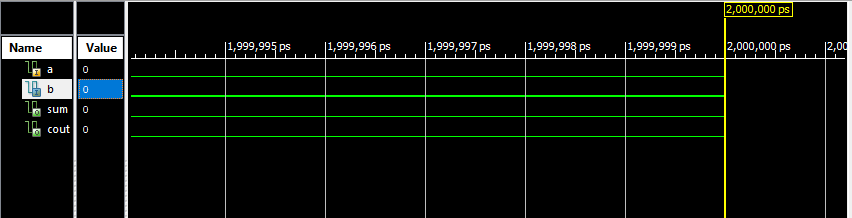

حالت اول: اگر ورودیها را a=0 و b=0 بدهیم، میبینیم که خروجی sum=0 و cout=0 میشود.

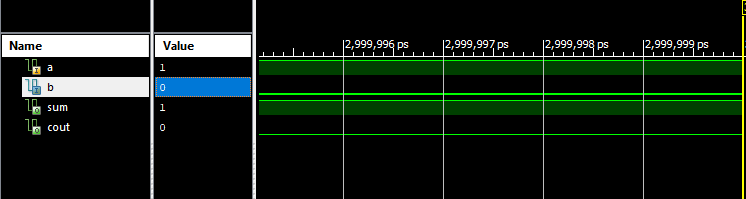

حالت دوم: اگر ورودیها را a=0 و b=1 بدهیم؛ میبینیم که خروجی sum=1 و cout=0 میشود.

حالت سوم: اگر ورودیها را a=1 و b=0 بدهیم؛ میبینیم که خروجی sum=1 و cout=0 میشود.

حالت چهارم: اگر ورودیها را a=1 و b=1 بدهیم؛ میبینیم که خروجی sum=0 و cout=1 میشود.

مقایسهی VHDL با زبان C

- منبع: ترجمه از سایت javatpoint.com

- منبع: عکس شاخص از سایت udemy.com

برای تهیه (ترجمه، ویرایش و انتشار) آموزش VHDL سه نفر زحمت کشیدن لطفا کپی نکنید. اگر این آموزش براتون مفید واقع شده ما را نیز دعا کنید و اگر خواستین میتوانید از محتوای رایگان آموزشی حمایت مالی کنید. همچنین اگر به زبان Verilog هم علاقمند هستید توصیه میکنیم مقاله آموزش FPGA و Verilog برای تازه کارها! را هم که شامل شش قسمت است مطالعه کنید. در ادامه یک مقاله دیگر و تکمیلتری از آموزش VHDL را منتشر خواهیم کرد که به مفاهیم مختلف و ساختار و دستوراتش بیشتر میپردازد.

اگر این نوشته برایتان مفید بود لطفا کامنت بنویسید.

آموزش طراحی و ساخت پروژه های الکترونیک و برنامه نویسی میکروکنترلر ها آموزش الکترونیک,آموزش رزبری پای,آموزش راه اندازی ماژول و سنسور,آموزش آردوینو,نرم افزار های الکترونیک, طراحیPCB,برنامه نویسی میکروکنترلرها ARM AVR PIC FPGA

آموزش طراحی و ساخت پروژه های الکترونیک و برنامه نویسی میکروکنترلر ها آموزش الکترونیک,آموزش رزبری پای,آموزش راه اندازی ماژول و سنسور,آموزش آردوینو,نرم افزار های الکترونیک, طراحیPCB,برنامه نویسی میکروکنترلرها ARM AVR PIC FPGA

ممنونم شما رو دعا کردم

با سلام و عرض ادب خیلی لطف فرمودین شکر میکنم که انسانهایی مثل جنابعالی وجود دارید