سنتز مدار

قبل از شروع درس این جلسه، اجازه دهید با هم آنچه را که در سه جلسهی قبلی این مجموعه آموزش آموختیم مرور کنیم. پس از مقدمات اولیهی بحث، ابتدا قدری با زبان سختافزاری وریلاگ آشنا شدیم و سپس یاد گرفتیم که چطور در این زبان ماژول طراحی کنیم. همچنین در جلسهی قبل آموختیم که چگونه ماژول طراحی شده را شبیهسازی (سیموله) کنیم. گفتیم که سیمولیشن به ما کمک میکند از صحت یا عدم صحت عملکرد مدار اطلاعات خوبی بدست آوریم. اما با این حال، سیمولیشن هرچقدر هم اطلاعات خوبی در مورد مدارمان به ما بدهد، باز هم همانطور که از اسم آن پیداست؛ فقط یک شبیهسازی است و نه اجرای مدار بر روی محیط (سختافزار) واقعی. تمام الکترونیک کارها این نکته را به خوبی میدانند که از شبیهسازی تا عمل هم چالشهای بسیاری ممکن است وجود داشته باشد. لذا تا زمانیکه در عمل هم نتایج صحیح نگیریم نمیتوانیم از صحت مداری که طراحی کردهایم خاطرجمع باشیم.

در این جلسه قرار است به همین موضوع بپردازیم. مراحل لازم برای سنتز مدار دیجتالی که تا مرحلهی شبیهسازی را از سر گذرانده است. برای پیادهسازی هم از بورد Mimas V2 Spartan 6 FPGA Development Board و یا Elbert V2 Spartan 3A FPGA Development Board استفاده میکنیم.

در جلسهی گذشته اشاره کوتاهی به این نکته کردیم که کدی که برای test bench استفاده میشود تنها در مرحلهی سیمولیشن قابل استفاده است و برای سنتز کردن مدار یا ماژول، باید آن را حذف کنیم و برای آن دسته از دوستانمان که ممکن است تا امروز با واژهی سنتز مدار آشنایی نداشته باشند هم این توضیح را اضافه کنیم که منظور از سنتر کردن یک کد نوشته شده به زبانهای سختافزاری (HDL)، مرحلهای است که کد نوشته شده به هرکدام از زبانهای HDL (مثلا Verilog یا VHDL یا …) توسط مفسرهای سختافزاری خوانده و تفسیر میشود و در صورت نبودن هیچ مشکلی، یک توپولوژی معادل سختافزاری برای آن کد تولید میشود. (چیزی شبیه مرحلهی کامپایل کردن کدهای نرمافزاری به زبانهای c یا …) باید توجه داشت که این توپولوژی سختافزاری تولید شده، بسیار متناسب و متناظر با نوع FPGAای که انتخاب کردهایم است و نمیتوان گفت که یک چیز یکتاست.

البته جزئیات داخلی پروسهی سنتز بسیار پیچیده و وقتگیر است و ما اصلا نمیخواهیم وارد آنها شویم. فعلا در حدی که بتوانیم ماژول کوچک طراحی شدهی خودمان را سنتز کنیم کفایت میکند.

ما در اینجا از بورد Mimas V2 Spartan 6 FPGA Development Board برای پیادهسازی استفاده میکنیم و مراحل را مطابق آن توضیح میدهیم. اما اگر بورد شما Elbert V2 Spartan 3A FPGA Development Board باشد نیز مراحل با تغیرات بسیار کمی همینها هستند و میتوانید دنبال کنید.

بورد Mimas V2 دارای Xilinx Spartan 6 FPGA وDDR SDRAM و تعدادی لوازم جانبی دیگر است.

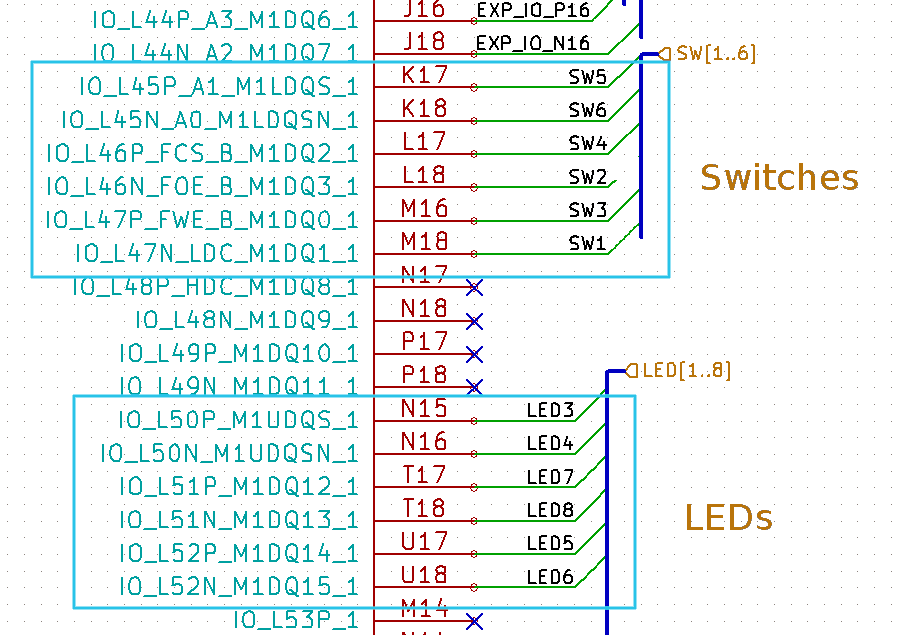

نام دقیق FPGA استفاده شده بر روی این بورد XC6SLX9-CSG324 است. این IC از نوع تراشههای BGA از سری CSG324 است که دارای 324 پین و 9K سلول منطقی است. تصویر زیر بخشی از شماتیک این FPGA را نشان میدهد که مربوط به قسمت ورودی/خروجیهای LEDها و سوییچهاست.

ما از یک کلید فشاری و یک LED برای پیادهسازی مدارمان استفاده خواهیم کرد.

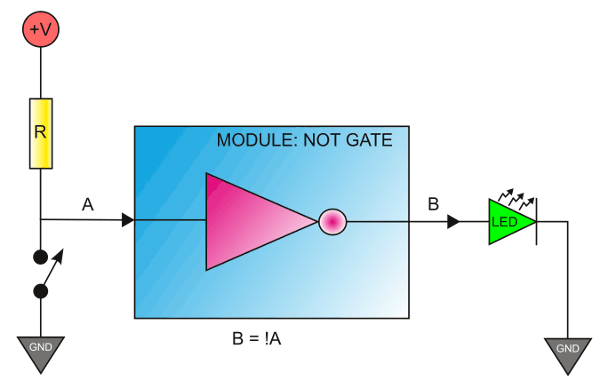

اما بیایید به ماژول خودمان برگردیم و به این فکر کنیم که چطور میتوانیم چیزی شبیه به آن را در سختافزار پیادهسازی کنیم. ماژول ما یک گیت NOT یا همان اینورتر بود. همانطور که میدانیم خروجی این ماژول همواره معکوس شدهی ورودی آن است. پس حالا که تا این اندازه ساده است، احتمالا پیکربندیهای مداری زیادی را بتوانیم برای تست عملکرد آن داشته باشیم و سادهترین چیزی که به ذهن میرسد مدار کلید و LED است. مداری که در تصویر زیر پیشنهاد شده است را ببینید.

در مدار فوق؛ یک کلید را میبینیم که با یک مقاومت پول آپ (pull up) به منبع VCC وصل شده است. از طرفی خروجی نیز به یک LED متصل است. خب، بیایید یک لحظه به این فکر کنیم که این مدار قرار است چه رفتاری از خود نشان بدهد؟ زمانیکه سوییچ باز است، ما یک ولتاژ مثبت در ورودی A خواهیم داشت. یعنی به لحاظ منطقی ورودی 1 وارد اینورتر میشود. به تبع آن خروجی اینورتر یعنی نقطهی B، منطق 0 را خواهیم داشت و این یعنی LED خاموش خواهد ماند.

حالا اگر سوییچ بسته شود، در ورودی گیت معکوسکننده ورودی 0، و در نتیجه در خروجی آن 1 خواهیم داشت. و این یعنی روشن شدن LED .

بسیار خب؛ حالا که سادهترین حالت مدار را برای پیادهسازی سختافزاری گیت NOT پیدا کردیم و دانستیم که به چه چیزی احتیاج داریم؛ نیازهای سختافزاری ما از این قرار است:

- یک کابل I/O برای ورودی همراه با یک مقاومت پول آپ و یک سوییچ.

- یک کابل I/O برای خروجی همراه با یک LED برای اتصال به آن.

حالا به سراغ بوردی که در اختیار داریم برویم: Mimas V2 Spartan 6 FPGA Development Board.

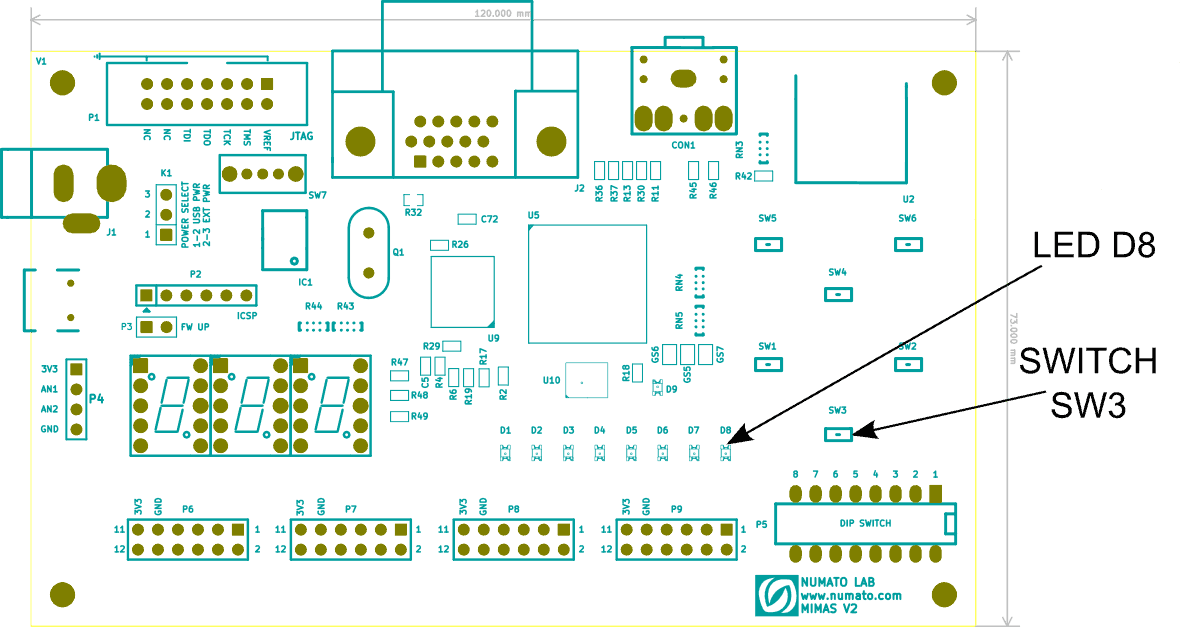

تصویر زیر بخش LEDها و سوییچهای آن را نشان میدهد و نیز آن LED و سوییچی که ما قصد داریم از آنها استفاده کنیم را هم مشخص کرده است. (Elbert V2 هم دقیقا به همین ترتیب یک بخش مربوط به LED و سوییچها را بر روی خود دارد. اگر از این بورد استفاده میکنید LED8 و Switch SW5 انتخابهای خوبی هستند و در آخر خبر خوش اینکه همین پروژه در حالیکه بر روی بورد Elbert V2 انجام شده است را نیز در انتهای این آموزش قرار دادهایم، شما میتوانید آن را دانلود کنید تا اگر به مشکلی برخوردید به آن مراجعه کنید.)

همانطور که در تصویر بالا میبینیم، Mimas V2 دارای 6 عدد کلید فشاری همه منظوره (GP) و 8 عدد LED است. اگر قدری در این شماتیک دقیقتر شویم تا این بورد را بیشتر و بهتر بشناسیم؛ علیالخصوص در مورد نحوهی اتصالات بخش سوییچ وLEDها، میبینیم که براساس جزییات داخلی این شماتیک، سوییچ SW5 به IO M16 متصل است، LED D8 نیز به T18. (البته T18 و M16 نام IOهای FPGA نیستند، دقیقتر اگر بخواهیم بگوییم، نام برجستگیهای DGA روی محفظه هستند که IOها به آنها متصل میشوند)

یکبار دیگر مرور کنیم که تا اینجا چه چیزهایی داریم، یک ماژول وریلاگ که میخواهیم آن را به صورت سختافزاری پیادهسازی کنیم و همچنین پلتفرم سختافزاری دلخواهمان را هم انتخاب کردهایم و میدانیم که بر روی این سختافزار با چه قسمتها و چه IOهایی قرار است کار داشته باشیم و به چه شکل میخواهیم از آنها استفاده کنیم.

در اینجا یکبار دیگر کدی که برای ماژول وریلاگمان نوشتیم را با هم مرور میکنیم.

module myModule(A, B); input wire A; output wire B; assign B = !A; endmodule

ماژول ما دو پورت دارد، پورت A به عنوان ورودی و پورت B به عنوان خروجی. در اینجا یک خوانندهی با دقت احتمالا این سوال به ذهنش میرسد که چطور میخواهیم پورت A ماژول را به پورت M16 سختافزار و پورت B آن را به پورت T18 متصل کنیم.

این کار را از طریق تعریف یک سری قوانین انجام میدهیم. این قوانین به بخشهای مسیریابی (routing) و جانمایی (placement logic) که هر دو جزئی از مراحل سنتز هستند میگوید که هرکدام از سیگنالهای ماژول را به کدام پورت فیزیکی باید متصل کنند.

تمام این قوانین را به صورت یک لیست نوشته، آنها را در یک فایل قید میکنیم و آن فایل را درون پروژه قرار میدهیم. به چنین فایلی User Constraints File گفته میشود. در ابزارهای مربوط به Xilinx فرمت آن به صورت یک text file با پسوند ucf. است. خبر خوب اینکه فایل های user constraint برای Mimas V2 به صورت آماده بر روی سایت آن قابل دانلود هستند و شامل تعریف تمام IOهای Mimas V2 میباشند. ما در این پروژه به تمام IOها احتیاج نداریم پس موارد اضافی را پاک کردهایم و مواردی که لازم هستند را در اینجا با هم میبینیم.

# User Constraint File for NOT gate implementation on Mimas V2

# Onboard LEDs

NET “LED” LOC = T18;

# Push Button Switches.

# Internal pull-ups need to be enabled since

# there is no pull-up resistor available on board

NET “SW” PULLUP;

NET “SW” LOC = M16;

محتوای این فایلها نیازی به توضیح چندانی ندارند و خودشان تا اندازهی خوبی قابل فهم هستند. مثلا در خط سوم میگوید که net LED را به پین واقعی T18 وصل کن. منظور از net چیست؟ معادل همان اتصال یا سیم در مدارهای واقعی است. پس یعنی سیم مربوط به LED را به پین T18 وصل کن، به همین راحتی.

یا مثلا در خط هفتم اگر به عبارت NET “SW” PULLUP دقت کرده باشید، احتمالا میتوانید حدس بزنید که منظور این است که سیم سوییچ باید پول آپ شود؛ یعنی با مقاومت به Vcc متصل شود و نکتهی جالب دیگری که خوب است در اینجا بدانید این است که در اغلب FPGAها، پورتهای IO خودشان مقاوت پول آپ دارند و نیازی به استفاده از مقاومت اضافی نیست. برای فعال کردن مقاومت پول آپ تعبیه شده در مسیر خودشان، کافیست در قوانین User Constraints File به آن اشاره کنیم. مثلا در همین خط هفتم که کلمهی Pull Up دقیقا به همین منظور به کار برده شده است و در واقع رسالت این خط و این دستور دقیقا فعال کردن همین مقاومت پول آپ در مسیر این اتصال است.

در خط یازدهم هم همانطور که میبینیم قید شده است که سر دیگر سوییچ به پورت M16 متصل شود والبته با همهی این توضیحات هنوز هم جای این سوال باقیست که پورتهای ماژول چطور قرار است به سوییچ و LED متصل شوند؟

یکبار دیگر یادآوری کنیم که وقتی میگوییم پورتهای ماژول، معادل این است که بگوییم سیمهایی که وارد ماژول میشوند یا از آن خارج میشوند. یعنی همان تعبیر NET که در بالا به کار بردیم. پس میتوانیم به همان ترتیب فوق، نام پورتها را با کلمهی کلیدی NET استفاده کنیم تا بتوانیم اتصالات آنها را هم ساماندهی کنیم.

بنابراین اگر همان فایل بالا را متناسب با گیت اینورتر خودمان ادیت کنیم، چنین چیزی خواهیم داشت.

# User Constraint File for NOT gate implementation on Mimas V2

# Onboard LEDs

NET “B” LOC = T18;

# Push Button Switches.

# Internal pull-ups need to be enabled since

# there is no pull-up resistor available on board

NET “A” PULLUP;

NET “A” LOC = M16;

باز هم یادآوری میکنیم که این پروژه به صورت کامل بر روی دو بورد Mimas V2 و Elbert V2 انجام شده و فایلهای آنها در انتهای این آموزش قابل دانلود است. ucf فایلها هم در درون آنها وجود دارد.

بسیار خوب، حالا هرچیزی که برای سنتز و تست سختافزاری مدارمان نیاز داشتیم را داریم و میدانیم.

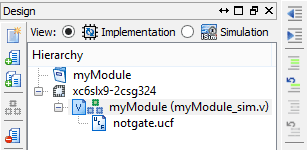

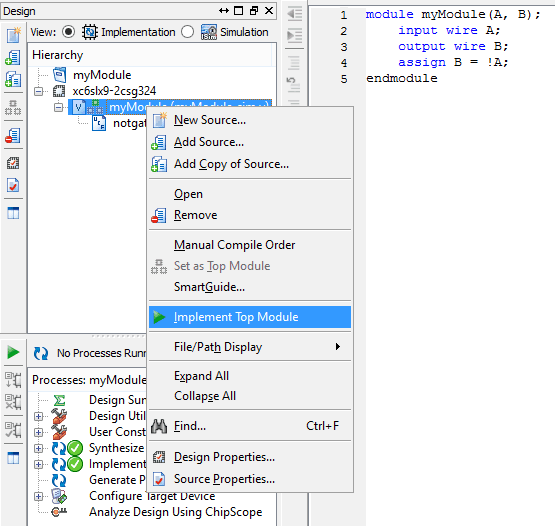

پروژهی سیمولیشنی را که در Xilinx ISE Webpack ایجاد کرده بودیم، باز میکنیم، مود را از همان مسیری که جلسه قبل گفتیم به Implementation mode تغییر میدهیم و ucf فایل را نیز مطابق تصویر زیر به پروژه اضافه میکنیم. ضمنا باز هم تاکید میکنیم که فراموش نکنید که کد قسمت مربوط به test bench را هم در سورس فایل وریلاگ پاک کنید.

پروژه را ذخیره کنید و بر روی ماژول راست کلیک کنید و از منوی ظاهر شده گزینهی Implement Top Module را انتخاب کنید. پروسهی سنتز ممکن است از چند دقیقه تا چند ثانیه طول بکشد و اگر همه چیز به خوبی پیش برود شما در حین پروسه، در پایین صفحه، در قسمت Process view که دقیقا زیر بخش Hierarchy view است، تعدادی دایرهی سبز رنگ میبینید که یک علامت تیک نیز بر روی آنها خورده است. (تصویر زیر را ببینید)

اگر هر کدام از آیتمها از رنگ سبز به رنگ زرد تغییر کند، معنایش آن است که در آن بخش یک هشدار( warning) وجود دارد و البته هشدارها به خودی خود و تا زمانیکه هشدار باشند احتمالا مشکلی ایجاد نمیکنند اما اگر از رنگ زرد به رنگ قرمز تغییر کنند معلوم است که در آنجا ایرادی وجود دارد، پس باید به عقب برگردید و مراحل را چک کنید تا اشکال پیدا و برطرف شود.

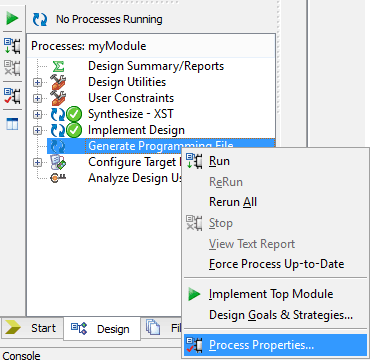

در اینجا میبینیم که ما طراحیمان را با موفقیت سنتز کردهایم و حالا نوبت آن است که سختافزاری که داریم را با خروجی حاصل شده برنامهنویسی کنیم. بورد ما که Mimas V2 و یا Elbert V2 است، خروجی پروسهی سنتز را که به آن bitstream گفته میشود، تنها با فرمت باینری قبول میکند. از طرفی ISE به صورت پیشفرض دادهها را در قالب باینری خالص تولید نمیکند، بنابراین باید تنظیمات این تبدیل را خودمان انجام دهیم. برای این کار مراحل زیر را دنبال میکنیم.

- در پنجرهی Processes بر روی Generate Programming File کلیک راست کنید.

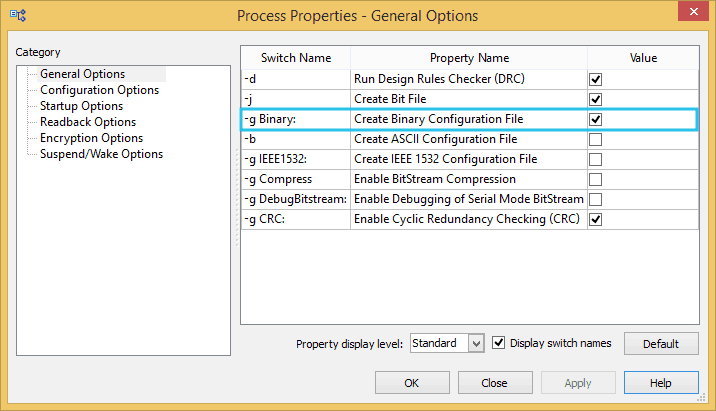

- از منوی ظاهر شده گزینهی Process Properties را انتخاب کنید و در پنجرهی باز شده، Create Binary Configuration File را تیک بزنید و سپس apply را بزنید.

- OK را بزنید تا پنجره بسته شود. مجددا بر روی Generate Programming File کلیک راست کنید و این بار RUN را انتخاب کنید. حالا اگر به مسیر ذخیره فایلهای پروژه بروید، فایل bin. تولید شده را خواهید دید. فایلی که به راحتی و به صورت مستقیم در Mimas V2 قابل استفاده است.

حالا در بورد FPGA، فایل myModule.bin را دانلود کنید. (اگر همهی مراحل به درستی انجام شده باشند این فایل در مسیر ذخیرهی فایلهای پروژه قرار دارد) اگر در مورد Mimas V2 به اطلاعات بیشتری نیاز داشته باشید میتوانید به دفترچهی راهنمای آن مراجعه کنید. نحوهی دانلود خروجی باینری بر روی آن نیز در آنجا توضیح داده شده است. زمانیکه دانلود تکمیل شد، کلید SW3 را فشار دهید و در این لحظه LED D8 روشن خواهد شد.

پروژهی کامل این پیادهسازی بر روی mimas V2 را از اینجا دانلود کنید.

پروژهی کامل این پیادهسازی بر روی Elbert V2 را از اینجا دانلود کنید.

- منبع: ترجمه از سایت numato.com

- منبع: عکس شاخص از سایت alamy.com

اگر آموزش آموزش FPGA و Verilog – سنتز مدار براتون مفید واقع شده ما را نیز دعا کنید و اگر خواستین میتوانید از محتوای رایگان آموزشی حمایت مالی کنید. همچنین نظرات، پیشنهادات و درخواستهای خود را در کامنتها ⇓ بنویسید.

اگر این نوشته برایتان مفید بود لطفا کامنت بنویسید.

آموزش طراحی و ساخت پروژه های الکترونیک و برنامه نویسی میکروکنترلر ها آموزش الکترونیک,آموزش رزبری پای,آموزش راه اندازی ماژول و سنسور,آموزش آردوینو,نرم افزار های الکترونیک, طراحیPCB,برنامه نویسی میکروکنترلرها ARM AVR PIC FPGA

آموزش طراحی و ساخت پروژه های الکترونیک و برنامه نویسی میکروکنترلر ها آموزش الکترونیک,آموزش رزبری پای,آموزش راه اندازی ماژول و سنسور,آموزش آردوینو,نرم افزار های الکترونیک, طراحیPCB,برنامه نویسی میکروکنترلرها ARM AVR PIC FPGA