DDR SDRAM

زمانیکه یک بورد FPGA را انتخاب میکنیم، یکی از مهمترین فاکتورهایی که باید مدنظر قرار گیرد میزان فضای ذخیرهسازی است. بوردهای مختلف، میتوانند انواع مختلفی از مموریها را داشته باشند. مثلا حافظههای SRAM ،QDR ،SDRAM و FLASH و …

- توصیه میکنم مقاله انواع حافظهها را مطالعه کنید.

DDR SDRAM یکی از محبوبترین انواع مموریهاست که حجم قابل قبول و بالایی از حافظهی فرار (volatile storage) را ارائه میدهد و دسترسی به آن نیز در زمان معقولی انجام میشود.

لازم است تذکر دهیم که وجود یک حافظهی فرار آنبورد در کاربردهای بسیاری مانند جمعآوری داده (data logging)، پردازش تصویر و … تا چه اندازه میتواند مهم و کلیدی باشد چرا که بلوک RAM موجود بر روی خود بوردهای FPGA محدود است و پاسخگوی نیاز چنین کاربردهایی نیست.

در این آموزش ما بنا نداریم که به اصول و معماری SDRAM بپردازیم، بلکه میخواهیم در قالب انجام یک پروژهی کوچک ببینیم که چگونه میتوان از DDR SDRAM استفاده کرد و آن را به FPGA (به طور خاص Xilinx Spartan 6) متصل نمود و البته در صورتی که علاقهمند باشید مقالات آموزشی در مورد ساختمان و عملکرد داخلی SDRAMها نیز به وفور در اینترنت قابل دسترسی هستند. از نظر ما این مجموعهی آموزشی اطلاعات کامل و جامعی در این زمینه ارائه نموده است که میتوانید در فرصت مناسب به سراغ آن بروید اما تاکید میکنیم که برای آنکه بتوانید پروژهی این جلسه را دنبال کنید اصلا نیازی نیست که به تئوریهای عملکردی SDRAMها به طور دقیق و عمیق مسلط باشید.

در این جلسه ما از بورد Numato Lab’s Mimas V2 FPGA Development Board استفاده خواهیم کرد. اما جای نگرانی نیست و برای سایر بوردها هم همین مراحل را با اعمال تغییراتی اندک میتوان اجرا نمود.

اما برای آنکه بتوانیم در بوردهای FPGA از SDRAM استفاده کنیم به چیزهایی نیاز خواهیم داشت.

- Memory Controller (کنترلر حافظه)

- Wrapper logic (منطق پوششدهی)

- User logic (منطق کاربر)

Memory controller قسمتی از مدار است که میتواند مستقیما با DRAM صحبت کند و سیگنالهای کنترلی لازم برای این ارتباط را نیز تولید میکند. مثلا سیگنالهای Address ،Data ،Control و … این کنترلر را یا میتوان از طریق نوشتن کدهای مربوطه پیادهسازی کرد و یا اینکه از قبل به صورت یک بلوک آماده در بورد تعبیه شده باشد.

اما در توضیح بیشتر حالت اول باید بگوییم که برخی از FPGAها هستند که مموری کنترلر را به صورت یک قطعهی سختافزاری و فیزیکال در دورن خودشان ندارند و تنها راه ایجاد چنین چیزی (ارتباط با DRAM) در آنها این است که کدهای کنترلر را به صورت دستی و با استفاده از امکانات و قابلیتهای موجود در FPGA بنویسیم. بدیهی است که چنین کاری بخشی از حافظهی قابل استفادهی FPGA را به خود اختصاص خواهد داد، حافظهای که در غیر این صورت میتوانست صرف اهداف دیگری شود. همچنین عملکرد چنین حالتی در مقایسه با FPGAهایی که مموری کنترلر را به صورت یک IP مجزا و تعبیه شده در درون خودشان دارند، طبیعتا ضعیفتر خواهد بود و البته خبر خوب این است که تعداد بالایی از انواع مختلف FPGAها امروزه این کنترلر را به صورت یک قطعهی درونی در خودشان دارند هرچند که به همین دلیل قیمت آنها نیز به نسبت بالاتر است، با این حال به نظر میرسد از آنجایی که این مدلها همانطور که توضیح دادیم عملکرد قابل قبولتری دارند، این اختلاف قیمت ارزشش را داشته باشد.

اما در اغلب مدلهای FPGAهایی که قابلیت مموری کنترلر را به صورت یک IP داخلی دارند، معمولا رابط کاربری این قطعه چندان برای استفادهی کاربران خوانا و روان نیست. به همین علت باید از یک قطعه کد wrapper یا پوشاننده استفاده شود که درست مانند یک واسط از یک سو با کنترلر ارتباط برقرار میکند (با منطق متناسب با آن) و از دیگر سو با یک رابط کاربری ساده و قابل فهم با قسمتهای منطق کاربری (user logic). این تعامل معمولا به صورت ارائهی پورتهایی برای نوشتن و خواندن از مموری کنترلر است. اما user logic که آخرین قطعهی پازل این ارتباط است، به تکه کدهایی گفته میشود که کار آنها تولید و مصرف دادههاست. مثلا ممکن است در حین سرو کله زدن با دادهها، در مواردی لازم شود که آنها را به صورت موقت بر روی SDRAM (یا هر نوع حافظهی دیگری که متناسب و موجود باشد) ذخیره کنند. به عنوان مثال یک سیستم جمعآوری داده یا دیتا لاگر را در نظر بگیرید که بر بستر FPGA پیادهسازی شده است. در حین کار ممکن است دادههایی را از ADC بخواند و آنها را در SDRAM ذخیره کند، بعدتر ممکن است این داده دوباره از SDRAM خوانده شود و برای مراحل بعدی به یک سیستم دیگر انتقال داده شود و تمام اینها یعنی تعامل دائمی و دو جانبه با حافظه.

احتمالا به این فکر میکنید که انجام دادن و پیادهسازی تمام این مراحل تا چه اندازه میتواند پیچیده باشد. حق با شماست اما نگران نباشید، ابزارهایی وجود دارند که طی این مسیر را برای ما به مراتب ساده خواهند ساخت. در واقع شرکت زایلینکس (Xilinx) در یک اقدام موثر و کاملا کارآمد در کنار تولید FPGAها، ابزارهای خیلی خوبی نیز تولید کرده است که با کمک آنها میتوانید تمام موارد بالا را با کمترین میزان کد نویسی در اختیار داشته و استفاده کنید. بنابراین جزئیات فوق را که ناظر به نیازمندیهای این ارتباط گفتیم را حتی میتوانید با خیال راحت فراموش کنید و هیچ دغدغهای در موردشان نداشته باشید. علت توضیح دادنشان نیز این بود که در آینده که در پروژههایی بخواهید از مموری کنترلر استفاده کنید، به این دانش حداقلی در موردشان نیاز خواهید داشت.

قبل از شروع پروژه، بیایید نگاه سریعی هم به بوردی که قرار است از آن استفاده کنیم بیندازیم. بورد Mimas V2 دارای یک FPGA از نوع Xilinx Spartan 6 LX9 است که با پکیج CSG324 ارائه میشود. این نوع FPGA دارای دو عدد مموری کنترلر است که درون آن تعبیه شده است. همچنین یک SDRAM با ظرفیت 512Mbit و از نوع LPDDR نیز دارد. اگر تا به حال نام LPDDR به گوشتان نخورده است باید بگوییم که LP مخفف Low Power و DDR از Double Data Rate گرفته شده است.

اما اینکه گفتیم پکیج و بستهبندی این FPGA از نوع CSG324 است، نکتهی مهمی است چرا که FPGAهای Xilinx Spartan 6 LX9 در بستهبندیهای دیگری نیز وجود دارند که هیچکدام از آنها دارای مموری کنترلر نیستند. پس دقت داشته باشید که ما حتما به این نوع نیاز داریم.

از این دو مموری کنترلری که درون FPGA وجود دارند، یکی از آنها به SDRAM متصل است و دیگری آزاد و بدون استفادهی پیشفرض نگه داشته شده است تا هر طور که کاربر نیاز داشته باشد از آن استفاده کند. تمام اتصالات و جزییات مربوط به اتصال کنترلر و SDRAM همگی در خود بورد لحاظ شدهاند و نیازی به اینکه ما بخواهیم در ضمن انجام پروژه وارد این ریزهکاریها بشویم یا از ابزارهای سختافزاری یا نرمافزاری خاصی برای اینکار استفاده کنیم نیست. اگر علاقهمند بودید که از چگونگی این اتصالات و ریزهکاریها سردربیاورید، شما را به صفحات آخر دفترچهی راهنمای بورد (User Manual)، قسمت شماتیک بورد Mimas و همینطور به فایل Xilinx Memory Interface Solutions User Guide ارجاع میدهیم و البته جدا از کنجکاوی یا عدم کنجکاوی در مورد این اتصالات، به شما توصیه میکنیم که در اولین فرصت حتما به این دو راهنمای ارزشمند سری بزنید زیرا اطلاعاتی به دست خواهید آورد که ورای انجام این پروژه نیز به کارتان خواهند آمد.

شرکت زایلینکس دو ابزار مختلف را برای پیادهسازی مدارهای طراحی شده بر روی Spartan 6 FPGAs ارائه کرده است که بسته به اقتضائات هر پروژه میتوانید از آنها استفاده کنید.

ISE برای طراحی و پیادهسازی مدارهای معمولی و EDK برای پیادهسازی سیستمهای نهفته (Embeded systems). همانطور که در جلسات قبل هم توضیح دادیم، در حالت ISE تمام کدها به صورت RTL کد مثلا Verilog و VHDL نوشته میشوند و در حالت EDK، ابتدا به کمک همان VHDL یک میکروپروسسور و پریفرالهای جانبی آن را بر روی FPGA ایجاد میکنیم (البته در برخی موارد حتی نیاز به نوشتن کد VHDL نیز نیست و به کمک ابزارهای اتوماتیک میتوان پروسسور را در FPGA ایجاد کرد) و سپس سیستم نهفته را با استفاده از زبانهای معمول میکروپروسسورها مثلا C، مینویسیم.

در این آموزش ما شیوهی کار با هردوی این محیطها (ISE و EDK) را بررسی میکنیم و برنامههایی را به عنوان نمونه در آنها اجرا میکنیم.

آشنایی با Help و تطبیق ورژن toolهای مورد استفاده

در این پروژه ما از ISE و EDK نسخهی 14.7 استفاده کردهایم و تمام عکسهایی که در ادامه از مراحل، نمایش خواهیم داد و نیز دستورات و … براساس محیط این ورژن است. اگر شما نسخهی دیگری داشته باشید ممکن است در برخی جزییات تفاوتهایی وجود داشته باشد که البته خودتان به سادگی میتوانید تفاوتها را تشخیص دهید و مراحل را با نسخهی مورد استفادهی خودتان سازگار کنید.

اگر احیانا هر گونه سوالی در مورد( ISE ،EDK (XPS/SDK ، میکروبلیز، Spartan 6 FPGA و … داشته باشید، بهترین و کاملترین help موجود صفحهی فروم شرکت زایلینکس است، forums.xilinx.com. یا مثلا میتوانید به دلخواه به صفحاتی مانند این بروید.

ایجاد، کانفیگوریشن و build کردن هستهی مموری کنترلر و تست کردن یک برنامه بر روی Xilinx ISE

برای انجام این پروژه به ابزارهای زیر نیاز داریم:

- Xilinx ISE Webpack (دانلود)

- Mimas V2 FPGA Development Board

- کابل USB

- Mimas V2 Configuration Tool (قابل دانلود از صفحهی شرکت زایلینکس)

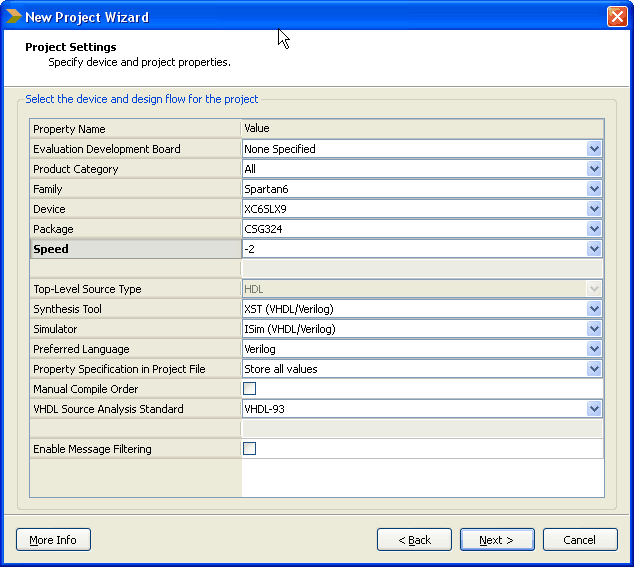

Xilinx ISE را باز کنید و از منوی فایل، new project را انتخاب کنید. در پنجرهی باز شده مطابق روال معمول در صفحهی اول نام پروژه و مسیر ذخیره شدن آن را وارد کنید. در صفحهی دوم FPGA مناسب را انتخاب کنید. یعنی همانطور که در تصویر زیر مشخص است کافیست که در قسمتهای Family ،Device و Package، به ترتیب Spartan6 ،LX9 (XC6SLX9) و CSG324 را انتخاب کنید. بقیه تنظیمات را هم مطابق تصویر زیر قرار دهید.

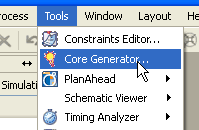

حالا next را بزنید تا پنجره بسته شود. خبر عجیب اما واقعی این است که قرار نیست ما هیچ source فایلی را به پروژه اضافه کنیم یا در آن تولید کنیم و کافیست IPها و سایر فایلهای مورد نیاز را با کمک Coregen tool تولید کنیم و پس از آن کارمان با ISE GUI تمام است. برای باز کردن Coregen tool هم به منوی Tools بروید و Core Generator را انتخاب کنید.

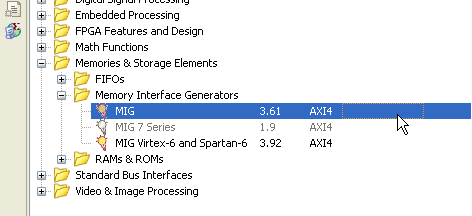

پروژهای به صورت خودکار ایجاد نشد، خودتان از طریق مسیر File > New Project آن را ایجاد کنید. زمانیکه میخواهید این کار را بکنید باید نوع FPGA و نوع پکیج آن را انتخاب کنید. در بخش design entry method هم Verilog را انتخاب کنید. با این کار مطمئن میشویم Coregen کدها را به زبان وریلاگ تولید میکند. حالا در پنجرهی MIG ،IP catalog را در یکی از زیرمجموعههای بخش Memory & Storage Elements پیدا کنید.

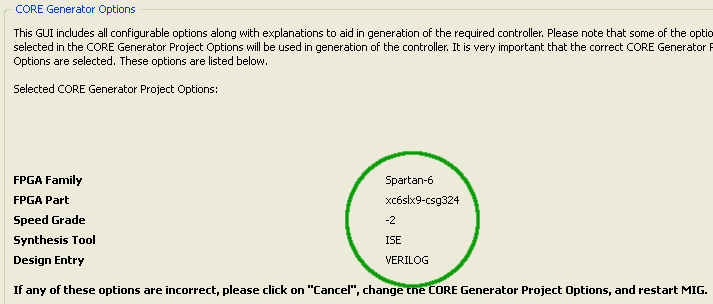

با دبل کلیک Memory Interface Generator wizard را راهاندازی کنید، در اولین صفحهای که مقابلتان باز میشود، اطمینان حاصل کنید که نوع FPGA و سایر تنظیمات به درستی انتخاب شده باشند. برای این کار از تصویر زیر کمک بگیرید و تنظیمات را مطابق آن قرار دهید.

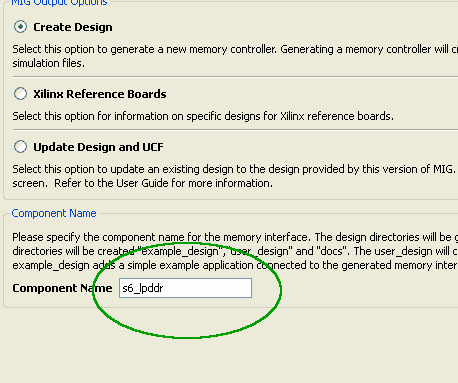

Next را بزنید تا به صفحهی بعدی بروید. هرکجا لازم بود نامی را وارد کنید، این کار را بکنید که البته حتی اگر روی همان نامهای پیشفرض هم بماند معمولا مشکلی ایجاد نمیکند. اما اگر دوست داشتید که همه چیز طبق نامگذاریهای خودتان شناخته شود، امکان تغییر دادن وجود دارد. مثلا ما در اینجا نام s6_lpddr را به عنوان نام بوردمان وارد میکنیم. اگر شما نام دیگری وارد کردید، در ادامهی آموزش هرکجا که به s6_lpddr برخورد کردید آن را با نام انتخابی خودتان جایگزین کنید.

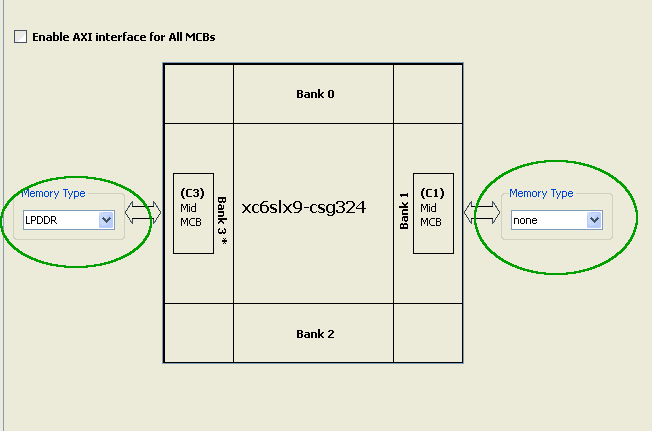

باز هم next را بزنید و به صفحهی سوم بروید. همهی گزینههای این صفحه را بدون تغییر رها کنید و به صفحهی چهارم بروید. در این قسمت میتوانیم نوع حافظهی DDR را انتخاب کنیم و به MIG بگوییم که این مموری به کجا متصل شده است. گفتیم که Spartan 6 LX9 دارای دو مموری کنترلر است. در بوردی که ما استفاده میکنیم، LPDDR به Bank 3 از FPGA وصل شده است. پس از لیست متناظر با Bank 3، نوع حافظه را LPDDR انتخاب کنید و به تنظیمات Bank 1 نیز کاری نداشته باشید. این توضیحات را میتوانید در عکس زیر ببینید که به چه شکل اعمال شدهاند.

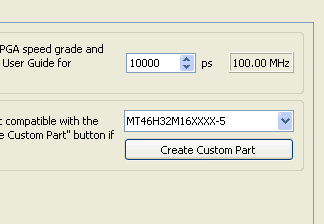

Next را بزنید و به صفحهی بعدی بروید. اینجا جایی است که DDR مموری و فرکانس کاری آن را تعیین میکنیم. گفتیم که حافظهی بورد Mimas V2 از نوع LPDDR است. نوع آن هم از Micron MT46H32M16 یا انواع دیگری که معادل همین عملکرد را داشته باشند است. این نوع حافظه از DDR clock تا 166MHz هم پشتیبانی میکند. پس در تنظیمات صفحهای که باز شده است؛ MT46H32M16 memory را انتخاب کنید و clock period را روی 10,000 تنظیم کنید. این مقدار معادل با 100MHz فرکانس DDR clock است. البته همانطور که گفتیم تا 166MHz را هم پشتیبانی میکند اما ما در اینجا چون نمیخواهیم در ادامه درگیر پیچیدگیهای تنظیمات PLL هم بشویم، همان 100MHz را انتخاب میکنیم. Mimas V2 یک سورس کلاک 100MHz دارد و زمانیکه ما هم برای DDR clock از همین فرکانس استفاده میکنیم، دیگر نیازی نیست که تنظیمات PLL را خودمان دستکاری کنیم و آن را با همان تنظیماتی که MIG برای آن به صورت پیشفرض قرار داده است، استفاده میکنیم. در تصویر زیر هم میتوانید ببینید که نوع مموری و فرکانس به همین صورت که توضیح داده شده انتخاب شدهاند.

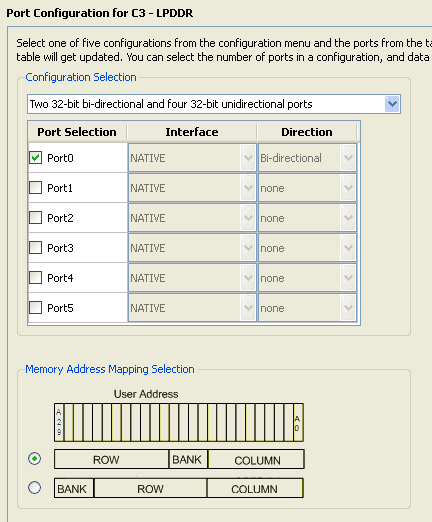

به مرحلهی بعد بروید و در صفحهی پیش رو هیچ کدام از تنظیمات را تغییر ندهید و همه را با همان مقادیر پیشفرض باقی بگذارید. باز هم next را بزنید و به صفحهی بعد بروید. این صفحه صفحهی تنظیمات مربوط به پورتهاست. مانند تصویر زیر، port 0 را تیک بزنید و بقیه را همانطور باقی بگذارید.

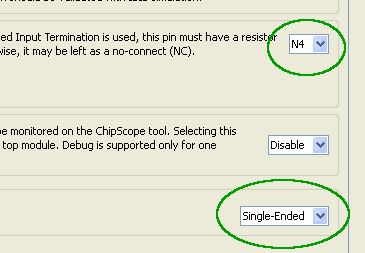

ادامه بدهید و به صفحهی بعدی بروید. از آنجایی که ما تنها از یکی از پورتها استفاده میکنیم، نیازی نیست که هیچکدام از تنظیمات این صفحه را تغییر دهیم. پس باز هم جلوتر میرویم تا به صفحهی FPGA Options screen برسیم. در بخشRZQ pin location، گزینهی N4 و در بخش system clock input، گزینهی Single Ended را انتخاب کنید. تصویر زیر به شما کمک خواهد کرد دقیقتر متوجه شوید.

حالا فقط کافی است چند بار دیگر next را بزنید تا به مرحلهی آخر برسید و در نهایت finish را بزنید تا پنجره بسته شود. پس از اتمام این مراحل Core Generator تعداد زیادی فایل تولید خواهد کرد که میتوانید به مسیر ipcore_dir\s6_lpddr\ رفته و پیدایشان کنید. (با این فرض که شما هم در مراحل قبل نام 6_lpddr را انتخاب کرده باشید در غیر این صورت باید نام انتخابی خودتان را در آدرس جایگزین کنید) وقتی که به این آدرس میروید، سه فولدر خواهید دید، docs ،example_design و user_design. درون فولدر docs تعدادی فایل مهم وجود دارد که میتوانید از آنها برای شناخت بیشتر مموری کنترلر Spartan 6 و IPهای ساخته شده توسط MIG استفاده کنید. حتما این نکته را در ذهن داشته باشید و در اسرع وقت این فایلها را بررسی کنید.

ویرایش user constraints

بسیارخب، در این مرحله میخواهیم یکی از example designهای تولید شده توسط MIG استفاده کنیم. این طراحیهای نمونه را همانطور که در خطوط پایانی بخش قبل توضیح دادیم، میتوانید در فولدر example design پیدا کنید. زمانیکه این پوشه را باز کنید، درون آن تعدادی فایل و فولدر دیگر خواهید دید. فولدر rtl تمام کدهای وریلاگ تولید شده توسط MIG را در درون خود دارد. فولدر par محتوی تعدادی فایل پچ و اسکریپت است که به کمک آنها میتوانیم طراحیها را build کنیم. در این میان user constraintها به صورت اتومات به گونهای ایجاد میشوند که با ابزارها و بوردهای خود شرکت زایلینکس مطابقت داشته باشند. اما برای هماهنگ شدن با Mimas V2 لازم است تغییراتی در آنها اعمال کنیم. کافیست قبل از build کردن پروژه مطابق دستورات زیر ویرایشهایی را انجام دهیم.

- فایل ucf را برای هماهنگ شدن با Mimas V2 ادیت میکنیم.

- build environment را به گونهای تنظیم میکنیم که یک کانفیگوریشن فایل باینری تولید کند.

به فولدر par بروید و در آنجا example_top.ucf را پیدا کنید. با استفاده از یک تکست ادیتور آن را باز کنید و تغییرات زیر را اعمال کنید.

- خط ;CONFIG VCCAUX=2.5 را بیابید و آن را به ;CONFIG VCCAUX=3.3 تغییر دهید. این تغییر بسیار حائز اهمیت است چرا که Mimas V2 برای VCCAUX از 3V استفاده میکند.

- خطوط زیر را هم تغییر دهید.

NET “error” IOSTANDARD = LVCMOS18;

NET “calib_done” IOSTANDARD = LVCMOS18;

NET “calib_done” LOC = “B2” ;

NET “error” LOC = “A2” ;ToNET “error” IOSTANDARD = LVCMOS33;

NET “calib_done” IOSTANDARD = LVCMOS33;

NET “calib_done” LOC = “T18” ; #LED1

NET “error” LOC = “T17” ; #LED2

تغییرات فوق باعث میشوند که پینهای «error» و «calib_done» براساس LVCMOS33 IO standard عمل کنند و همچنین اتصالات مربوط به نتهای T18 و T17 از FPGA را که LEDهای 1 و 2 به آنها متصل هستند را تنظیم میکند. به این ترتیب زمانیکه کالیبراسیون انجام شد LED1 و زمانیکه تست کردن مموری با خطا مواجه شد LED2 روشن خواهند شد.

- خطوط زیر را تغییر دهید.

NET “c3_sys_rst_n” IOSTANDARD = LVCMOS18;ToNET “c3_sys_clk” IOSTANDARD = LVCMOS33;

NET “c3_sys_rst_n” IOSTANDARD = LVCMOS33;

این تغییرات ورودی کلاک را براساس IOهای استاندارد تنظیم میکنند و ورودی را نیز به LVCMOS33 بازنشانی (ریست) میکنند. باز هم به این دلیل که این IOها به bank تعلق دارند که با ولتاژ 3.3V تغذیه میشود.

- خط ;NET “c3_sys_rst_n” PULLDOWN را اضافه کنید.

با این کار reset pin را پول داون میکنیم و به این ترتیب ریست شدن مموری کنترلر بدون نیاز به تجهیزات یا کار اضافهای در اختیار و کنترل ما خواهد بود و البته برخلاف آنچه که از ظاهر نام «c3_sys_rst_n» برمیآید، MIG ورودی ریست را به صورت active high قرار میدهد.

- «c3_sys_clk» و «c3_sys_rst_n» را هم به شکل زیر تغییر دهید.

NET “c3_sys_clk” LOC = “V10” ;

NET “c3_sys_rst_n” LOC = “M16” ;

با این کار IO pad مناسب را به ورودی کلاک و SW3 را هم به عنوان ورودی ریست اختصاص میدهیم.

تا اینجا تمام تغییراتی که باید در ucf فایل میدادیم را انجام دادهایم. اگر خواندن اینها شما را کمی گیج کرده و احساس میکنید که چقدر کار مشکلی در پیش رو دارید، به شما اطمینان میدهیم که اگر در عمل دقت کافی به خرج دهید پیچیدگی چندانی نخواهد داشت و به خوبی از پس آن برخواهید آمد. به عنوان یک پیشنهاد به شما توصیه میکنیم که همیشه ابتدا از فایل ucf اصلی یک بکآپ ذخیره کنید تا در صورتی که نیاز بود ویرایش را از اول آغاز کنید به مشکل برنخورید.

Build کردن کد

در قدم بعدی به سراغ build environment میرویم و آن را به گونهای اصلاح میکنیم که یک کانفیگوریشن فایل باینری تولید کند. این مرحله از مرحلهی قبلی نیز به مراتب سادهتر است. فایل mem_interface_top.ut را پیدا کنید و آن را در یک تکست ادیتور دلخواه باز کنید. خط«g Binary:no-» را بیابید، آن را به «g Binary:yes-» تغییر دهید، فایل را ذخیره کنید و ببندید.

بسیار خب، حالا همه چیز آماده است که پروژه را build کنیم. فقط قبل از شروع مطمئن شوید که مسیر منتهی به Xilinx build tools به درستی به PATH environment variable اضافه شده باشد. معمولا این مسیر به صورت زیر است.

C:\Xilinx\\ISE_DS\ISE\bin\nt (با این فرض که ISE بر روی درایو C نصب شده باشد)

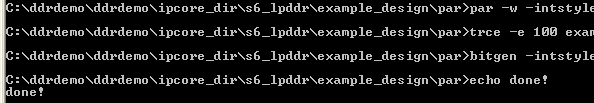

حالا بچ فایل با نام ise_flow.bat را با دبل کلیک کردن روی آن اجرا کنید. (میتوانید از command prompt هم برای باز کردن آن استفاده کنید) اگر همه چیز تا این مرحله به درستی انجام شده و پیش رفته باشد، بچ فایل به طور اتومات تمام toolهای لازم برای build شدن پروژه را اجرا میکند و در نهایت شما باید یک پیغام Done دریافت کنید و پس از آن میبینید که در فولدر par تعدادی فایل جدید ایجاد شدهاند. پیغامی که دریافت میکنید شبیه تصویر زیر است.

اگر فرآیند build شدن با اشکال مواجه شود یا اصطلاحا fail شود، برای آنکه متوجه شوید علت خطا چه بوده به فایل ise_flow_results.txt مراجعه کنید. همچنین اگر build با موفقیت انجام شود فایل example_top.bin را نیز باید در فولدر par مشاهده کنید. این همان فایلی است که میخواهیم بورد program Mimas V2 Spartan 6 FPGA development board را با آن برنامهریزی کنیم.

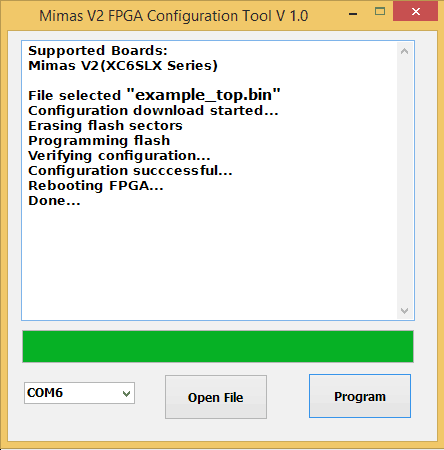

کانفیگور کردن بورد Mimas V2 و تست کردن آن

پروگرم کردن این بورد بسیار ساده است. آخرین ورژن Configuration Downloader Application را از سایت خود محصول دانلود کنید. فایل اجرایی را باز کنید (نیازی به نصب نیست) فایل باینری ساخته شده در مرحلهی قبل را لود کنید و مانند تصویر زیر پروگرم کردن را شروع کنید.

log window را با دقت بررسی کنید و مطمئن شوید که configuration binary file با موفقیت دانلود شده است.

خب، حالا میخواهیم تست کنیم که آیا مموری اینترفیسها به درستی کار میکنند یا خیر. اگر به یاد داشته باشید، در قسمتهای قبلی فایل ucf را در برخی قسمتها ویرایش کردیم. دو تا از خطوطی که تغییر دادیم را در زیر مشاهده میکنید.

NET “calib_done” LOC = “T18” ; #LED1

NET “error” LOC = “T17” ; #LED2

در خط اول پین T18 از FPGA را به سیم calib_done متصل کردیم و در خط دوم پین T17 را به سیم error. از طرفی این پینهای FPGA به ترتیب متناظر با LED1 و LED2 هستند. برای آنکه بتوانیم عملکرد صحیح example program که اجرا کردهایم را تایید کنیم، کافیست چک کنیم که LED متصل به calib done؛ یعنی LED1، پس از راهاندازی بورد روشن میشود یا خیر. روشن شدن آن به این معناست که کالیبراسیون اولیه به درستی انجام شده و LED متصل به سیم error (یعنی LED2) نیز خاموش است.

اگر این واکنش، یعنی روشن شدن LED1 و خاموش ماندن LED2 پایدار بماند و تا لحظات قابل قبولی تغییر نکند، نشاندهندهی این است که پروژهی آزمایشی شما تا اینجا به درستی کار میکند و البته جا دارد که از Xilinx Memory Interface Generator نیز تشکر کنیم که کدهای کامل و آماده را در اختیار ما قرار داده است.

ایجاد، کانفیگوریشن و build کردن هستهی مموری کنترلر و تست کردن یک برنامه بر روی Xilinx EDK

دیدیم که تولید و build کردن یک پروژهی سادهی آزمایشی که میتواند با استفاده از DDR SDRAM ،ISE را تست کند، ساده و هیجانانگیز بود. خبر خوبی که وجود دارد این است که میتوان حتی تمام مموری را هم تست کرد و خروجی را به وسیلهی UART چاپ کرد. این کار با کمک Xilinx EDK امکانپذیر است و حتی از کار کردن با ISE نیز هیجانانگیزتر است.

مثلا میتوانید کدهای سادهای را با زبان C بنویسید و به حافظهی (DDR SDRAM) دسترسی پیدا کنید (مموری اکسس). با ادامهی آموزش همراه باشید تا به شما یاد بدهیم که چگونه میتوان تمام این کارها را انجام داد.

برای انجام دادن این پروژه به ابزارهای زیر نیاز خواهیم داشت.

- Xilinx EDK (برای اطلاعات بیشتر میتوانید اینجا کلیک کنید)

- Mimas V2 FPGA Development Board

- کابل USB

- Mimas V2 Configuration Tool (قابل دانلود از سایت محصول)

میکروبلیز چیست؟

میکروبلیز (Microblaze) یک soft processor IP سی و دو بیتی است که توسط شرکت زایلینکس و برای FPGAهای رده بالا و میانردهی آنها طراحی شده است. با بوردهای Spartan 6 ،Virtex و Zynq سازگار است و البته میتوانید به سایت شرکت زایلینکس بروید و در صفحهی مربوط به میکروبلیز، دیتاشیتهای مختلفی برای این پروسسور پیدا کنید. خبر خوب این است که نیازی نیست این پروسسور را به صورت جداگانه دانلود کنیم، چرا که همراه با Xilinx EDK tool و به صورت یک پک ارائه شده است که قبلا آن را دانلود کردهایم. (اگر دانلود نکرده باشید، باید حتما این کار را انجام دهید) embedded system که بر پایهی پروسسور میکروبلیز طراحی میشود، میتواند از AXI و یا PLB به عنوان باس سیستم استفاده کند اما از آنجایی که برنامهی آیندهی شرکت زایلینکس این است که به مرور باس سیستم PLB را از رده خارج کرده و تنها AXI را نگه دارد، پس بهتر است که ما هم از همان AXI استفاده کنیم و در نهایت بهتر است خیالتان راحت باشد، برای انجام دادن این پروژه اصلا نیازی نیست که در حال حاضر دانش عمیقی درمورد AXI و میکروبلیز داشته باشید. آن مقداری که نیاز داریم را همینجا به شما توضیح خواهیم داد و برای مطالعات بیشتر میتوانید خودتان بعدا اقدام کنید.

AXI چیست؟

AXI خلاصه شدهی عبارت Advanced eXtensible Interface (اینترفیس توسعهپذیر پیشرفته) است. یک باس سیستم برای اتصالات داخلی که براساس معماری باس محبوب ARM، یعنی AMBA طراحی شده است. در یک embedded system که بر پایهی پروسسور میکروبلیز توسعه داده میشود، از AXI استفاده میکنیم که میکروپروسسور را به تمام پریفرالهای موجود در آن سیستم متصل کنیم. در این میان تنها یک استثنا وجود دارد و آن Block RAM است که برای اتصال دادن آن با میکروپرسسور از LMB (Local Memory Bus) استفاده میکنیم.

نسخهی AXILite هم ارائه شده است که از آن برای اتصال دادن پریفرالهایی که throughput پایینی دارند استفاده میشود. به عنوان مثال UART ،GPIO و …

تفاوت آن با AXI در این است که AXILite در مقایسه با AXI، المانهای منطقی کمتری را از FPGA مصرف میکند و در نتیجه منابع بیشتری از FPGA برای سایر کارها در دسترس خواهد بود. بنابراین از خود AXI تنها در مواردی استفاده میکنند که بخواهیم پریفرالهای با throughput بالا مثلا DDR memory را اتصال دهیم یا مثلا ماژولهای Ethernet و مواردی از این قبیل.

در انتهای این معرفی، باز هم جا دارد تاکید کنیم که برای ادامهی این پروژه همینقدر اطلاع داشتن از AXI کفایت میکند و فعلا نیازی به اطلاعات جزئیتری ندارد. با این حال اگر هر زمان مشتاق یا نیازمند کسب اطلاعات دقیقتری در این مورد بودید از فایل AXI Reference Guide که از اینجا قابل دسترسی است، استفاده کنید.

EDK چیست؟

مجموعهای از ابزارهای توسعه (development tools) که توسط شرکت زایلینکس و با این هدف ارائه شدهاند که کمک کنند بتوانیم بر پایهی پروسسور میکروبلیز، Embedded system طراحی کنیم یا اینکه بتوانیم نرمافزار این سیستمها را ارتقا دهیم. Xilinx EDK دو جزء اساسی دارد.

- Xilinx Platform Studio (XPS)

- Xilinx Software Development Kit (SDK)

XPS و SDK دو ابزار نرمافزاری جداگانه هستند که از آنها استفاده میکنیم که سیستمها را طراحی و سپس پیادهسازی کنیم.

XPS را برای طراحی سیستمهای سختافزاری استفاده میکنیم و SDK ابزاری است که به کمک آن برای میکروبلیز پروسسور نرمافزار مورد نظرمان را مینویسیم.

با کمک XPS میکروبلیز پروسسور و تنظیمات آن و پریفرالهای لازم را انجام میدهیم و از طراحیمان یک bit فایل تولید میکنیم. این bit فایل را برای برنامهریزی FPGA استفاده میکنیم.

نرمافزاری که در SDK مینویسیم میتواند به زبان C یا ++C باشد.

در نهایت XPS و SDK به کمک هم تمام هدر فایلها و اسکریپتهای مرتبط کنندهای (linker scripts) را که برای build شدن سیستم شما مورد نیاز هستند، تولید میکنند. در ادامهی آموزش همینطور که پروژه جلو میرود جزییات بیشتری از این دو ابزار را خواهیم آموخت. با این حال اگر دوست داشتید کاملتر در موردشان بدانید اینجا برای شما فایلهای خوبی در دسترس خواهد بود.

ایجاد پلتفرم سختافزاری نهفته بر بستر میکروبلیز پروسسور

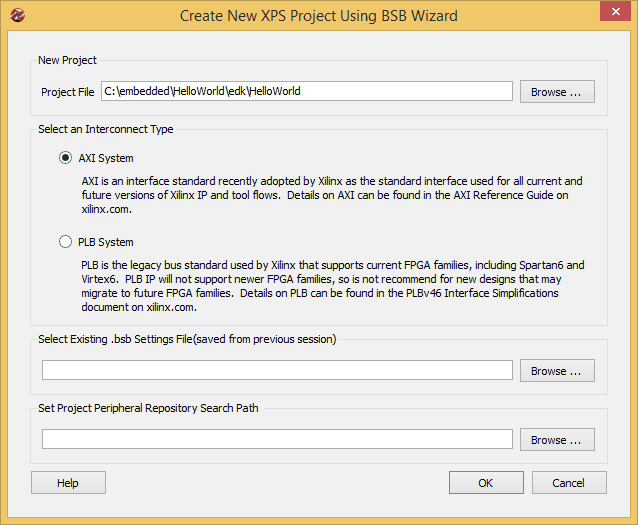

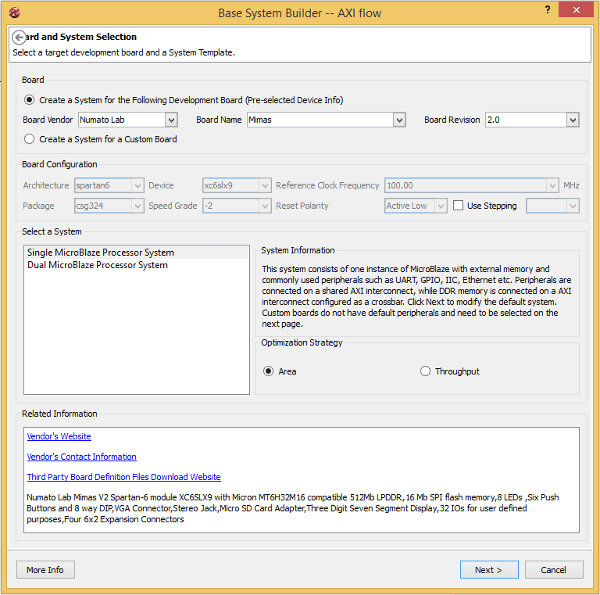

در این قسمت میخواهیم با هم یاد بگیریم که چگونه یک Embedded Platform ساده را با استفاده از XPS و بر پایهی میکروبلیز ایجاد کنیم. برای ساخت این سیستم از base System Builder (BSB) wizard استفاده خواهیم کرد و برای این کار باید ابتدا فایل های BSB System Wizard را از صفحهی سایت آن دانلود کنید و آنها را در آدرس C:\Xilinx\xx.xx\ISE_DS\EDK\board اکسترکت کنید. زمانیکه این کار را کردید آدرس نهایی فایل باید به صورت C:\Xilinx\xx.xx\ISE_DS\EDK\board\NumatoLab\ipxact\MimasV2\data در بیاید. اگر همینطور بود و مشکلی وجود نداشت، به مسیر All Programs > Xilinx Design Tools > EDK بروید و از آنجا بر روی آیکون XPS کلیک کنید. پس از اینکه لود شد، بر روی New BSB Project که در زیر منوی فایل قرار دارد کلیک کنید (و یا اینکه Ctrl+Shift+B را بزنید تا BSB wizard فراخوانی شود) اگر همه چیز خوب پیش رفته باشد، پنجرهی BSB Wizard مطابق تصویر زیر در مقابل شما باز خواهد شد.

آدرسی فولدری که میخواهید پروژه را در آنجا ذخیره کنید و نیز نامی را برای پروژه انتخاب و وارد کنید. در قسمت Interconnect Type گزینه AXI System را انتخاب کنید و Ok را بزنید. در صفحهی بعدی، در بخش board Vendor combo، گزینهی Numato Lab را انتخاب کنید. (این بخش تنها در صورتی فعال خواهد بود که فایلهای پشتیبان BSB Wizard برای Mimas V2 را به درستی و مطابق مرحلهی قبل در مسیر گفته شده قرار داده باشید) در بخشهای Board Name و Board Version به ترتیب Mimas و 2.0 را وارد کنید و به مرحلهی بعد بروید.

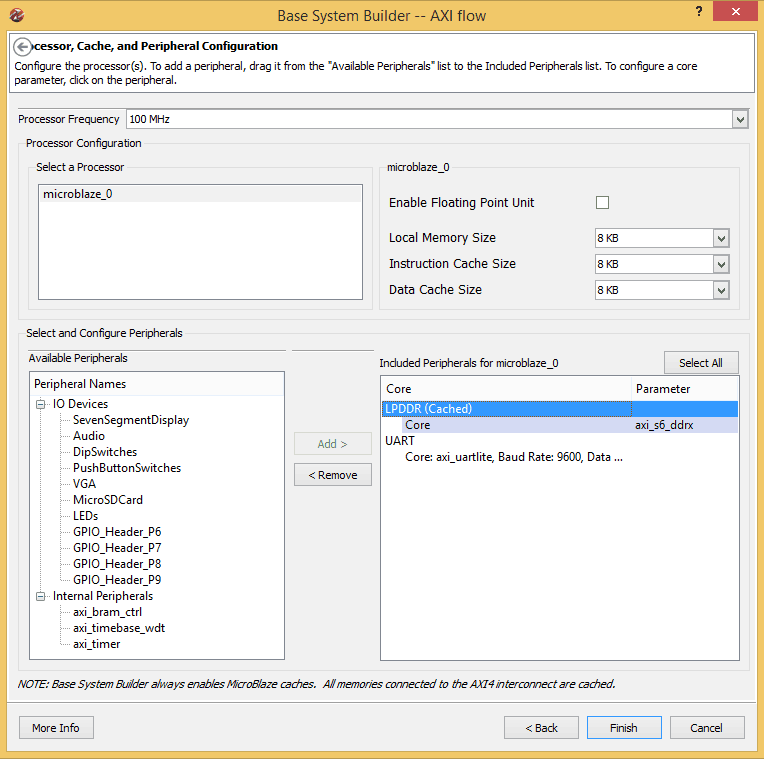

استراتژی اتخاذ شده برای اپتیمایز کردن طراحی را میتوانید روی Area یا Throughput قرار دهید. در این مثال ما آن را با انتخاب پیشفرض خودش یعنی Area جلو میبریم و تغییری نمیدهیم. به صفحهی بعدی بروید و همانطور که در تصویر زیر میبینید، در این صفحه میتوانیم پریفرالها را انتخاب کنیم.

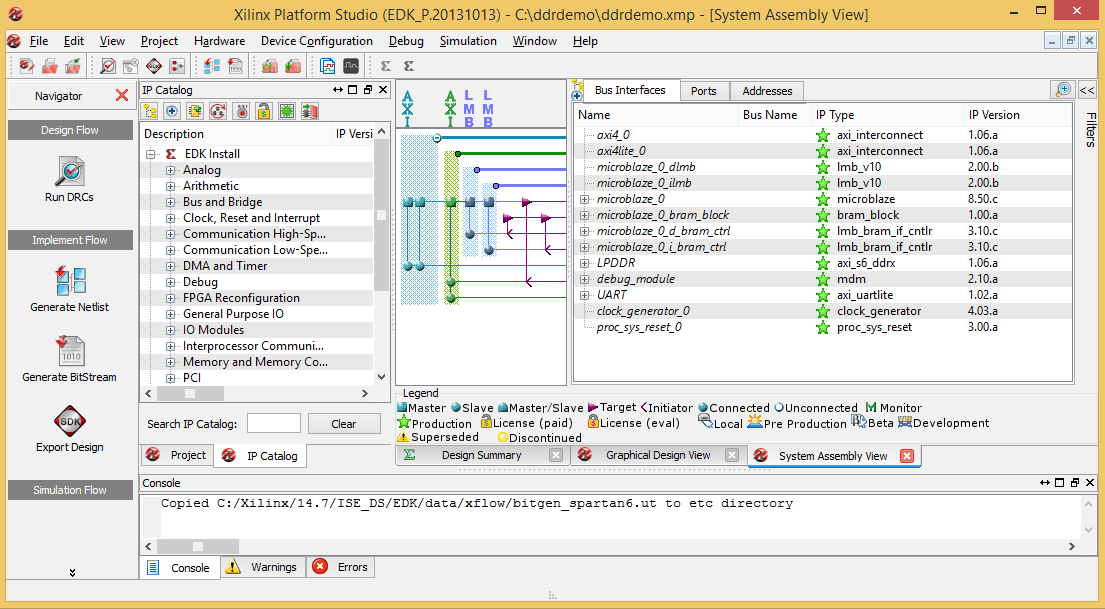

به هیچ چیز دست نزنید، و همه را در همان وضعیت دیفالتی که وجود دارند باقی بگذارید، Finish را بزنید که این مرحله خاتمه یابد. حالا XPS سیستم شما را ایجاد میکند و پنجرهای مطابق تصویر زیر در مقابل شما خواهد بود.

تمام IPهای موجود و استفاده شده در پنجرهی فوق وجود دارند. هم IPهایی که در طراحی از آنها استفاده شده است و هم تمام باسهایی که برای متصل کردن IPها به کار رفتهاند. همانطور که ممکن است دقت کرده باشید، میبینیم که DDR مموری و میکروبلیز پروسسور توسط AXI bus به هم متصل شدهاند که به علت نیاز بیشتر DDR به throughput است در حالیکه برای دیگر پریفرالها از AXILite استفاده شده است. حالا برای آنکه کاری کنیم که این سیستم بتواند بر روی Mimas V2 کار کند، باید یک سری تنظیمات انجام دهیم.

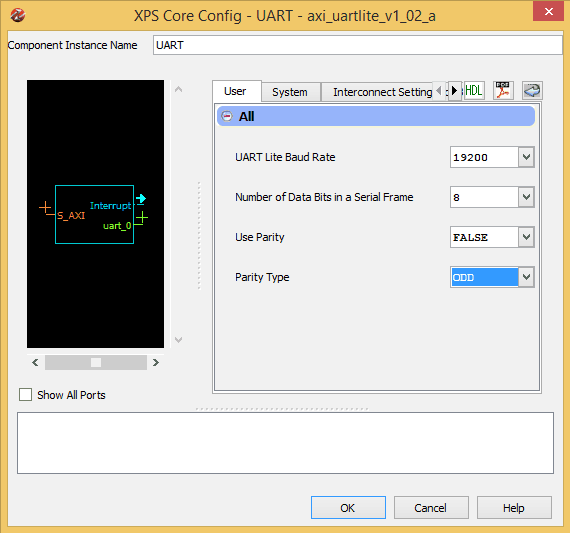

تغییر دادن baud rate

اولین چیزی که باید تغییر دهیم، بادریت UART است. در بخش Bus Interfaces بر روی UART IP کلیک راست کنید و Configure IP را انتخاب کنید. در پنجرهای که باز میشود بادریت را روی 19200 قرار دهید و بقیهی تنظیمات را دستکاری نکنید. این فرآیند در تصویر زیر نشان داده شده است.

متصل کردن RESET به یک سوییچ خارجی

در قدم بعدی باید یک سوییچ را به نت RESET میکروبلیز پروسسور تخصیص دهیم. با این کار میتوانیم هر زمان که نیاز باشد کل سیستم را ریست کنیم. اما چطور این کار را انجام دهیم؟ فایل ddrdemo.ucf را در project view باز کنید و در آن خط

NET “RESET” PULLUP;

را با

NET “RESET” LOC = M16 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST | PULLUP;

جایگزین کنید. به این ترتیب سوییچ SW3 از FPGA را به RESET اختصاص دادهایم. پس هر وقت SW3 را فشار دهیم، کل پروسسور ریست خواهد شد.

انتخاب CCLK به عنوان کانفیگوریشن کلاک

XPS به صورت دیفالت JTAG را به عنوان کلاک FPGA در نظر میگیرد. اگر ما از JTAG adapter مثلا از Xilinx Platform Cable – USB برای پروگرم کردن FPGA استفاده کرده باشیم، این حالت دیفالت بسیار خوب عمل خواهد کرد. اما حالا که از بورد Mimas استفاده میکنیم، باید به جای JTAGCLK از CCLK استفاده کنیم. برای اعمال این تغییر، در محیط XPS به تب Project که دقیقا در کنار تب IP Catalog قرار دارد بروید و فایل Bitgen Options را باز کنید (etc/bitgen.ut). در آنجا «g StartUpClk:JTAGCLK-» را پیدا کنید و آن را با «g StartUpClk:CCLK-» جایگزین کنید. فایل را ذخیره کنید و بر روی گزینهی Generate Bitstream در سمت چپ را انتخاب کنید تا سیستم کامپایل و bitstream تولید شود. براساس سرعت هر کامپیوتر این فرآیند ممکن است از دو یا سه دقیقه الی چند ده دقیقه طول بکشد. زمانیکه bit file با موفقیت ساخته شد، در جعبه ابزار سمت چپ صفحه Export Design را بزنید و در پنجرهای که باز میشود Export Only را انتخاب کنید. این مرحله تمام فایلهای مورد نیاز برای ساخت یک پروژهی SDK را به یک مسیر مناسب اکسپورت میکند. (معمولا به SDK\SDK_Export\hw که در زیرمجموعههای فولدر اصلی ذخیرهی پروژه قرار دارد)

در این لحظه سیستم سختافزاری ما آماده است. اما اگر کمی گیج شدهاید که سیستم سختافزاری یعنی چه؟ مجددا یادآوری میکنیم که چیزی که ما الان در دست داریم شبیه این است که یک میکروکنترلر/ میکروپروسسور در اختیار داشته باشیم که آماده است برای آن کد بنویسیم تا عمل بخصوصی را برای ما انجام دهد. حالا ما آن میکروکنترلر/ پرسسور را با استفاده از یک FPGA ساختهایم و قدم بعدی این است که برای این چیزی که ساختهایم کد بنویسیم و آن را راهاندازی کنیم.

نوشتن یک برنامهی کاربردی برای میکروبلیز پروسسور

برای نوشتن و کامپایل کردن کد برای پلتفرم سختافزاری که در قسمت قبل ساختیم، از SDK استفاده میکنیم.

Xilinx SDK یک IDE از نوع Eclipse-based است که قادر است برای پلتفرمهایی که بر بستر میکروبلیز ساخته شدهاند، برنامه نوشته، build و debug کند.

برای شروع به All Programs > Xilinx Design Tools > EDK بروید و Xilinx Software Development Kit یا همان SDK را باز کنید. اگر از شما سوال شد که یک workspace انتخاب کنید، مسیری را که ترجیح میدهید فایلهای پروژه در آنجا ذخیره شوند را وارد کنید.

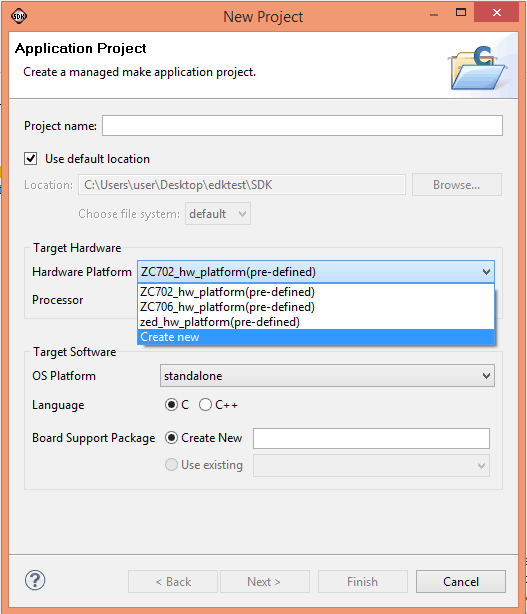

در محیط برنامه برای ایجاد یک پروژهی جدید از منوی فایل New Application Project را بزنید و پس از آن با پنجرهای مشابه تصویر زیر مواجه خواهید شد.

از لیست hardware platform، گزینه create new را بزنید. پنجرهی جدیدی باز خواهد شد که در آنجا میتوانید یک پلتفرم سختافزاری جدید ایجاد کنید.

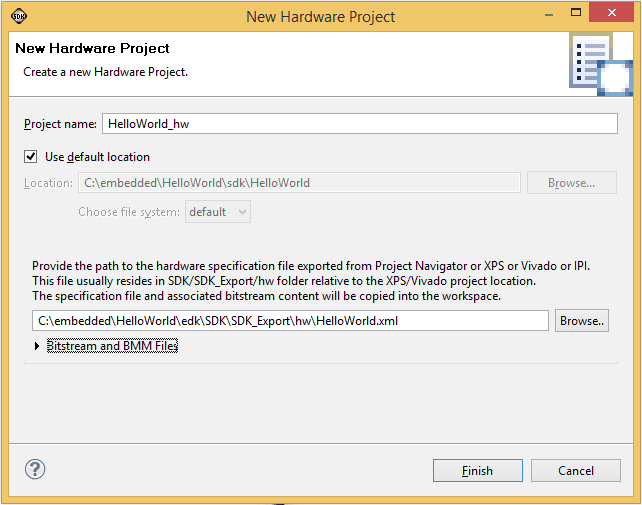

به بخش browse بروید و در آنجا مسیری که قبل فایلهای پروژهی XPS را در آن ذخیره کرده بودید را پیدا کنید. SDK\SDK_Export\hw را جستجو کنید و از آنجا ddrdemo.xml را انتخاب کنید. به صورت اتومات یک نام مناسب برای آن انتخاب خواهد شد و ما هم این نام را تغییر نمیدهیم. Finish را بزنید و مجددا به Application Project Wizard بازگردید.

نام پروژه را وارد کنید و بقیهی تنظیمات را مانند تصویر زیر تغییر ندهید.

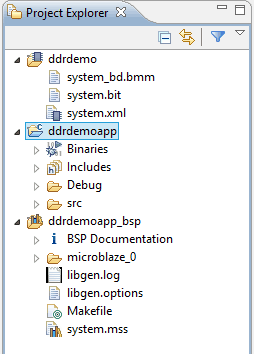

Next را بزنید و به آخرین صفحهی application project Wizard بروید. از لیست templateهای موجود Memory Test را انتخاب کنید و finish را بزنید. SDK محیط کار را ایجاد کرده و سه پروژه به آن اضافه میکند. تمام این پروژهها همانطور که در تصویر زیر نشان داده شده است در Eclipse Project Explorer قابل مشاهده هستند.

پروژهای که بالای بقیه قرار دارد hardware platform است. این فایلها مستقیما از آدرسی که XPS فایلهای سیستم سختافزاری را اکسپورت کرده بود، کپی میشوند. پروژهی بعدی application project است که مربوط به این مرحله است، یعنی نوشتن یک برنامهی کاربردی برای پلت فرم سخت افزاری ساخته شده و در نهایت آنکه در انتهای لیست قرار گرفته است پروژهی BSP است که به طور اتوماتیک توسط SDK تولید شده بود. کتابخانهها و فایلهایی که ممکن است نیاز داشته باشیم در این بخش قرار گرفتهاند.

برای build شدن پروژه از منوی Project، گزینه Build All را بزنید. اگر همه چیز به درستی انجام شده باشد بدون هیچ خطایی پروژه build خواهد شد.

باز هم یادآوری میکنیم که پروژهای که در اینجا استفاده میکنیم یک پروژهی آماده و قابل دانلود است که میتوان از آن برای تست کردن سختافزار ایجاد شده استفاده کرد. اگر دوست داشتید کد آن را ببنید به فولدر src در بخش ddrdemoapp project بروید و سورس فایلهای لیست شده را باز کنید. تابع main در memorytest.c قرار دارد.

پس از استفاده از این کد آزمایشی در صورتی که شما از صحت عملکرد پلتفرم سختافزاریتان مطمئن شدید، میتوانید با کدهایی که خودتان مینویسید نیز از آن استفاده کنید. (البته با اعمال تنظیمات متناظر با کد در ساخت پلتفرم)

Build و تست کردن برنامه

پس از اینکه پروژه با موفقیت ساخته میشود SDK خود، build کردن برنامه را برعهده خواهد گرفت، اما شما هم میتوانید با زدن Ctrl+B یا کلیک کردن روی Build All از منوی project، این وظیفه را مجددا به او یادآوری کنید.

در این مرحله که هم پروژهی XPS و هم پروژهی SDK را با موفقیت ایجاد کردهایم، وقت آن رسیده است که نسخهی باینری برنامهی نهایی را تولید کنیم. یک ایده این است که از ابزار Xilinx data2mem استفاده کنیم و bit فایلی که توسط XPS برای میکروبلیز تولید شده و نیز فایل اجرایی ساخته شده توسط SDK را با هم ترکیب (merge) کنیم.

برای این کار به سه فایل زیر احتیاج داریم.

- bit file (فایلی که اگر شما هم نامگذاریهایتان را مطابق با ما پیش رفته باشید اکنون با نام bit و احتمالا در آدرس SDK\SDK_Export\hw در داخل فولدر پروژهی XPS قرار دارد)

- فایل اجرایی (فایلی که اگر شما هم نامگذاریهایتان را مطابق با ما پیش رفته باشید اکنون با نام elf و در احتمالا در آدرس ddrdemoapp\Debug، داخل فولدر SDK workspace قرار دارد)

- .bmm file (فایلی که اگر شما هم نامگذاریهایتان را مطابق با ما پیش رفته باشید اکنون با نام bmm و احتمالا در آدرس SDK\SDK_Export\hw در داخل فولدار پروژهی XPS وجود دارد)

زمانیکه هر سه مورد این فایلها را در یک فولدر مشترک کپی کردید، command line prompt را باز کنید و به فولدر مذکور بروید. برای تولید فایل bin نهایی دو مرحلهی زیر را طی کنید.

قدم اول

cmd> c:\Xilinx\xx.x\ISE_DS\settings64.bat

cmd> data2mem -bm ddrdemo_bd.bmm -bd ddrdemoapp.elf -bt ddrdemo.bit

در دستور خط اول xx.x را با ورژن ISE خودتان تطبیق داده و جاگذاری کنید و در دستور خط دوم هم از نام درست پروژهها استفاده کنید (اگر نامگذاری شما با ما متفاوت بوده است)

دستورات که با موفقیت اجرا شوند، شما باید یک bit file جدید را ببینید که در فولدر اضافه شده است. (مثلا برای ما با نام ddrdemo_rp.bit است)

قدم دوم

حالا باید bin file را تولید کنیم. در همان command window، دستور زیر را اجرا کنید.

cmd> promgen -w -p bin -u 0x0 ddrdemo_rp.bit -spi -o download_me

اگر با موفقیت اجرا شد خواهید دید که تعدادی فایل جدید در فولدر اضافه شدهاند و یکی از آنها باید download_me.bin باشد. از آن برای کانفیگور کردن Mimas V2 استفاده میکنیم.

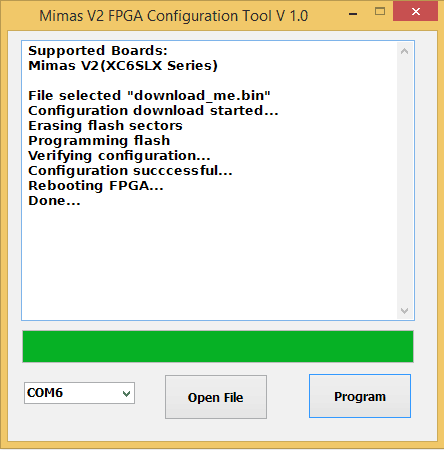

پس Mimas V2 flash configuration tool را اجرا کنید. (مطمئن شوید که سوییچ لغزان Mimas V2 در مود پروگرم کردن باشد و اگر به اطلاعات بیشتری نیاز دارید به سراغ دفترچهی راهنمای بورد بروید) download_me.bin را انتخاب کنید و program را همانند تصویر زیر بزنید.

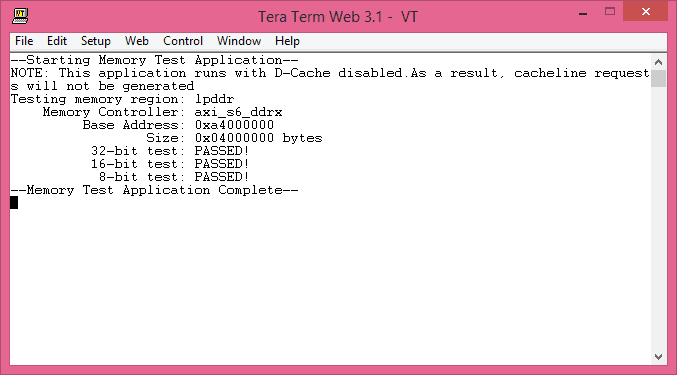

زمانی که بورد پروگرم شد، سوییچ لغزان را به مود نرمال بازگردانید و با استفاده از نرمافزارهای ارتباط سریالی مانند Hyperterminal یا TeraTerm، به پورت COM بورد متصل شوید. سپس سوییچ SW3 را بزنید تا پروسسور ریست شود. اگر مشکلی وجود نداشته باشد، باید ببینیم که نتایج تست به صورت زیر بر روی ترمینال نمایش داده شدهاند.

این آموزش نشان داد که برخلاف تصور اولیه ی بسیاری از ما، چقدر ساده میتوان برنامههای ساده و آزمایشی برای DDR SDRAM که در Mimas V2 FPGA Development Board وجود دارد نوشت و با آن ارتباط برقرار کرد. (و یا هر بورد دیگری از خانوادهی Spartan 6 که همین مموری را داشته باشد) بنابراین معطل نکنید و دست به کار شوید، پروژههای پیشرفتهتر هم چندان ترسناک نخواهند بود.

- منبع: ترجمه از سایت numato.com

- منبع: عکس شاخص از سایت alamy.com

اگر آموزش آموزش FPGA و Verilog برای تازه کارها – DDR SDRAM براتون مفید واقع شده ما را نیز دعا کنید و اگر خواستین میتوانید از محتوای رایگان آموزشی حمایت مالی کنید. همچنین نظرات، پیشنهادات و درخواستهای خود را در کامنتها ⇓ بنویسید.

اگر این نوشته برایتان مفید بود لطفا کامنت بنویسید.

آموزش طراحی و ساخت پروژه های الکترونیک و برنامه نویسی میکروکنترلر ها آموزش الکترونیک,آموزش رزبری پای,آموزش راه اندازی ماژول و سنسور,آموزش آردوینو,نرم افزار های الکترونیک, طراحیPCB,برنامه نویسی میکروکنترلرها ARM AVR PIC FPGA

آموزش طراحی و ساخت پروژه های الکترونیک و برنامه نویسی میکروکنترلر ها آموزش الکترونیک,آموزش رزبری پای,آموزش راه اندازی ماژول و سنسور,آموزش آردوینو,نرم افزار های الکترونیک, طراحیPCB,برنامه نویسی میکروکنترلرها ARM AVR PIC FPGA